# Godson 3A1000 Processor User Manual

# volume One

$\label{eq:condition} \mbox{Multi-core processor architecture, register description and system software programming guide} \\ \mbox{V1.15}$

2015 Nian 09 Yue

Loongson Zhongke Technology Co., Ltd.

1

## Copyright Notice

The copyright of this document belongs to Loongson Zhongke Technology Co., Ltd. and reserves all rights. Without written permission, any company and individual No one may publicize, reprint or otherwise distribute any part of this document to third parties. Otherwise, the law will be investigated Legal responsibility.

#### Disclaimer

This document only provides periodic information, and the content can be updated at any time according to the actual situation of the product without notice. Ruin The company does not assume any responsibility for direct or indirect losses caused by improper use of documents.

## Loongson Zhongke Technology Co., Ltd.

Loongson Technology Corporation Limited

Address: Building 2, Longxin Industrial Park, Zhongguancun Environmental Protection Technology Demonstration Park, Haidian District, Beijing Building No. 2, Loongson Industrial Park,

Zhongguancun Environmental Protection Park, Haidian District, Beijing

Telephone (Tel): 010-62546668

Fax: 010-62600826

# Page 3

## Reading guide

"Godson 3A1000 Processor User Manual" is divided into the first and second volumes.

"Loongson 3A1000 Processor User Manual" is divided into two parts, the first part (Chapter 1 ~ Chapter 10) introduces Loongson

3A1000 multi-core processor architecture and register description, on chip system architecture, function and configuration of main modules, registers

Lists and bit fields are explained in detail; the second part (Chapter 11 ~ Chapter 16) is the system software programming guide

Special presentations on common problems in the operating system development process.

The second volume of the "Loongson 3A1000 Processor User Manual" introduces in detail the adoption of Loongson 3A1000 from the perspective of system software developers

GS464 high-performance processor core.

# Page 4

# revise history

Document name: Godson 3A1000 Processor User Manual

Document update record --volume One

version number V1.15

founder: R & D Center

Creation Date: 2015-09-11

# Update history

| Serial numberdated |            | version nur | nber update content                                                                                                                                                                                                                                                       |

|--------------------|------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                  | 2009-10-30 | V1.0        | Increase the definition of DDR related parameters; modify the base address of UART and SPI                                                                                                                                                                                |

| 2                  | 2009-11-13 | V1.1        | Add definition of PCI_CONFIG to configuration pins                                                                                                                                                                                                                        |

| 3                  | 2010-06-25 | V1.2        | Add the second part of the manual, including the configuration and use of interrupts, serial port configuration and Use, EJTAG debugging instructions, address window configuration conversion, system memory space  Distributed design and memory allocation of X system |

| 4                  | 2010-06-29 | V1.3        | Revised Chapter 1 Overview, Chapter 2 Address Distribution                                                                                                                                                                                                                |

| 5                  | 2010-07-20 | V1.4        | Corrected some text errors in the HT configuration register                                                                                                                                                                                                               |

| 6                  | 2010-07-28 | V1.5        | Added Chip Config and Chip Sample register definitions in Section 10.5                                                                                                                                                                                                    |

| 7                  | 2010-12-17 | V1.6        | Revise the definition of DDR related parameters                                                                                                                                                                                                                           |

8 2011-11-24 V1.7 Edit cover

9 2012-02-14 V1.8 Increase CLKSEL setting limit

10 2012-02-23 V1.9 Add DDR configuration register interrupt vector description

2012-04-25 V1.10 Add detailed description of chip configuration register

11 Add detailed description of HT diagnostic register

2012-08-23 V1.11 revised DDR parameter definition

12 Add the definition of HT register supported by LS3A1000E

$13\ 2012\text{-}10\text{-}30\ V1.12$  Added matrix handling register supported by LS3A1000E

2014-04-02 V1.13 According to the chip naming rules, Loongson 3A processor was renamed Loongson 3A1000

Organizer

15 2014-07-24 V1.14 Add industrial-grade chip content

16 2015-09-11 V1.15 Revise the description of GPIO configuration register

Page 5

Godson 3A1000 processor user manual directory

Manual feedback: service@loongson.cn

# Page 6

## Godson 3A1000 processor user manual directory

# table of Contents

| Godson 3A1000 Processor User Manual                                     | <u>I</u>     |

|-------------------------------------------------------------------------|--------------|

| first part 1                                                            |              |

| Multi-core processor architecture, register description                 | 1            |

| 1 Overview                                                              | <u> 2</u>    |

| 1.1 Introduction to Loongson series processors                          | <u> </u>     |

| 1.2 Introduction to Godson 3A1000                                       | 3            |

| 1.3 Description of Loongson 3A1000 Commercial and Industrial Chips      | 5            |

| 2 System Configuration and Control                                      | <u>6</u>     |

| 2.1 Chip working mode                                                   | <u> 6</u>    |

| 2.2 Description of control pins                                         | <u> 6</u>    |

| 2.3 Cache consistency                                                   | <u>8</u>     |

| 2.4 Physical address space distribution at the node level of the system | <u>8</u>     |

| 2.5 Address Routing Distribution and Configuration                      | 10           |

| 2.6 Chip Configuration and Sampling Register                            | <u>16</u>    |

| 3 GS464 processor core                                                  | <u> 19</u>   |

| 4 Secondary Cache                                                       | twenty one   |

| 5 Matrix processing accelerator                                         | twenty three |

| 6 Interruption and communication between processor cores                | 26           |

| 71/O interrupt                                                          | 28           |

| 8 DDR2 / 3 SDRAM controller configuration                               | 31           |

| 8.1 Overview of DDR2 / 3 SDRAM controller functions                     | 31           |

| 8.2 DDR2 / 3 SDRAM read operation protocol                              | 31           |

| 8.3 DDR2 / 3 SDRAM write operation protocol                             | 32           |

| 8.4 DDR2 / 3 SDRAM parameter configuration format                       | 32           |

| 9 HyperTransport Controller 7                                           | <u>6</u>     |

| 9.1 HyperTransport hardware setup and initialization                    | <u>76</u>    |

| 9.2 HyperTransport protocol support                                     | <u>78</u>    |

| 9.3 HyperTransport interrupt support                                    | <u>. 79</u>  |

| 9.4 HyperTransport Address Window 8                                     | <u>80</u>    |

|                                                                         |              |

Page 7

I

| 9.4.1 HyperTransport space                                            | <u>80</u>    |            |

|-----------------------------------------------------------------------|--------------|------------|

| 9.4.2 Internal window configuration of HyperTransport controller      |              | 80         |

| 9.5 Configuration Register                                            |              | 81         |

| <u>9.5.1 Bridge Control</u> <u>83</u>                                 |              |            |

| 9.5.2 Capability Registers 83                                         |              |            |

| 9.5.3 User-defined register                                           | <u> 85</u>   |            |

| 9.5.4 Receive Diagnostic Register                                     | 86           |            |

| 9.5.5 Interrupt routing mode selection register (LS3A1000E and above) | 87           |            |

| 9.5.6 Receive buffer initial register (LS3A1000E and above)           | 87           |            |

| 9.5.7 Receive Address Window Configuration Register                   |              | 87         |

| 9.5.8 Interrupt Vector Register                                       | 89           |            |

| 9.5.9 Interrupt enable register                                       | 91           |            |

| 9.5.10 Interrupt Discovery & Configuration                            |              |            |

| 9.5.11 POST address window configuration register                     |              | 93         |

| 9.5.12 Prefetch address window configuration register                 |              | 94         |

| 9.5.13 UNCACHE address window configuration register                  |              | <u> 95</u> |

| 9.5.14 HyperTransport bus configuration space access method           |              | 9 <u>6</u> |

| 9.6 HyperTransport multiprocessor support                             | 96           |            |

| 10 Low speed IO controller configuration                              |              | 99         |

| 10.1 PCI / PCI-X controller                                           | 99           |            |

| 10.2 LPC Controller                                                   | 103          |            |

| 10.3 UART Controller                                                  | 105          |            |

| 10.3.1 Data Register (DAT)                                            | <u>. 105</u> |            |

| 10.3.2 Interrupt Enable Register (IER)                                | 105          |            |

| 10.3.3 Interrupt Identification Register (IIR)                        |              | <u>105</u> |

| 10.3.4 FIFO Control Register (FCR)                                    | 106          |            |

| 10.3.5 Line Control Register (LCR)                                    | 107          |            |

| 10.3.6 MODEM Control Register (MCR)                                   | 10           | <u>18</u>  |

| 10.3.7 Line Status Register (LSR)                                     | 108          |            |

| 10.3.8 MODEM Status Register (MSR)                                    |              |            |

| 10.3.9 Frequency Division Latch                                       | 110          |            |

II

# Page 8

# Godson 3A1000 processor user manual directory

| 10.4 SPI controller 11              | <u>0</u> |

|-------------------------------------|----------|

| 10.4.1 Control Register (SPCR) 111  |          |

| 10.4.2 Status Register (SPSR) 111   |          |

| 10.4.3 Data Register (TxFIFO) 112   |          |

| 10.4.4 External register (SPER) 112 |          |

| 10.5 IO controller configuration    | 113      |

| the second part                     |          |

| System Software Programming Guide   | 118      |

| 11 Interrupt configuration and use  | 119      |

| 11.1 Interrupted flow                                                           | <u> 119</u> |

|---------------------------------------------------------------------------------|-------------|

| 11.2 Interrupt routing and interrupt enable                                     | 119         |

| 11.2.1 Interrupt routing 1                                                      | 120         |

| 11.2.2 Interrupt enable                                                         | 122         |

| 11.3 Interruption of distribution                                               | 123         |

| 12 Serial Port Configuration and Use                                            | 125         |

| 12.1 Optional serial port 12                                                    | <u>25</u>   |

| 12.2 Serial configuration of PMON                                               | 125         |

| 12.3 Serial Port Configuration of Linux Kernel                                  | <u>126</u>  |

| 13 EJTAG debugging                                                              | 128         |

| 13.1 Introduction to EJTAG                                                      | 128         |

| 13.2 Use of EJTAG tools                                                         | . 129       |

| 13.2.1 Environmental preparation                                                | 129         |

| 13.2.2 PC Sampling                                                              | 129         |

| 13.2.3 Read and write memory                                                    | 129         |

| 13.2.4 Implementation instructions                                              | 129         |

| 13.2.5 Online GDB debugging                                                     | 133         |

| 14 Address window configuration conversion                                      | 134         |

| 14.1 How to configure the address window of the first and second level crossbar |             |

| 14.2 Address window of primary crossbar                                         | 134         |

| 14.3 Timing of configuring the address window of the first-level crossbar       | 136         |

| 14.4 Address window of secondary crossbar switch                                | 136         |

|                                                                                 |             |

III

# Page 9

## Godson 3A1000 processor user manual directory

| 14.5 Special treatment for address window configuration                        | <u> 137</u> |     |

|--------------------------------------------------------------------------------|-------------|-----|

| 14.6 HyperTransport Address Window                                             | 138         |     |

| 14.6.1 External access window of processor core                                | 138         |     |

| 14.6.2 DMA access address window of external device to processor chip memory   | 139         |     |

| 14.6.3 Low-speed device address window                                         | 140         |     |

| 14.7 Example Analysis of Address Space Configuration                           | 140         |     |

| 14.7.1 Example 1 of primary crossbar                                           | 141         |     |

| 14.7.2 Example 1 of the first-level crossbar                                   | 142         |     |

| 14.7.3 Example of a two-level crossbar 1                                       | 143         |     |

| 14.7.4 Example 2 of a two-level crossbar                                       | 144         |     |

| 15 System memory space distribution design                                     | 146         |     |

| 15.1 System memory space                                                       | 146         |     |

| 15.2 Mapping relationship between system memory space and peripheral DMA space |             | 149 |

| 15.3 Other mapping methods of system memory space                              | 150         |     |

| 16 X system memory allocation                                                  | 151         |     |

IV

# Page 10

## Loongson 3A1000 processor user manual map directory

# Figure catalog

| Figure 1-1 Loongson No. 3 system structure                                       | <u>2</u> |            |

|----------------------------------------------------------------------------------|----------|------------|

| Figure 1-2 Loongson No. 3 node structure                                         | _3       |            |

| Figure 1-3 Godson 3A1000 chip structure4                                         |          |            |

| Figure 3-1 GS464 structure diagram 20                                            |          |            |

| Figure 7-1 Loongson 3A1000 processor interrupt routing diagram                   | 28       |            |

| Figure 8-1 DDR2 SDRAM row and column address and CPU physical address conversion |          | 31         |

| Figure 8-2 DDR2 SDRAM read operation protocol                                    | 32       |            |

| Figure 8-3 DDR2 SDRAM write operation protocol                                   | 32       |            |

| Figure 9-1 HT protocol configuration access in Loongson No. 3                    | 96       |            |

| Figure 9-2 Four-piece Loongson No. 3 interconnection structure                   |          | <u> 97</u> |

| Figure 9-3 Two-chip Loongson No. 3 8-bit interconnection structure               |          | <u>97</u>  |

| Figure 9-4 Two-chip Loongson No. 3 16-bit interconnection structure              |          | <u> 98</u> |

| Figure 10-1 Configure the read and write bus address generation                  | <u></u>  | 103        |

| Figure 11-1 3A-690e Interruption Flow Chart                                      |          |            |

| Figure 11-2 Schematic diagram of Loongson 3A1000 processor interrupt routing     |          | 120        |

| Figure 13-1 EJTAG debugging system                                               |          |            |

| Figure 16-1 The graphics card processing image display process                   |          | 151        |

V

# Page 11

## Godson 3A1000 processor user manual table entry

# Table directory

| Table 2-1 Control pin description6                                                            |             |              |

|-----------------------------------------------------------------------------------------------|-------------|--------------|

| Table 2-2 Node-level system global address distribution                                       | 8           |              |

| Table 2-3 Address distribution in nodes                                                       | <u> 9</u>   |              |

| Table 2-4 Address distribution in nodes                                                       | <u>9</u>    |              |

| Table 2-5 First-level crossbar address window register table                                  | 10          |              |

| Table 2-6 Correspondence between the labels and the modules at level 2 XBAR                   | <u></u>     | 13           |

| Table 2-7 The space access attributes corresponding to the MMAP field                         |             | 13           |

| Table 2-8 Secondary XBAR address window conversion register table                             | <u></u>     | 14           |

| Table 2-9 Secondary XBAR default address configuration                                        |             | <u> 16</u>   |

| Table 2-10 Chip Configuration Register (Physical Address 0x1fe00180)                          | 16          |              |

| Table 2-11 Chip sampling register (physical address 0x1fe00190)                               | <u> 17</u>  |              |

| Table 4-1 Secondary Cache Lock Window Register Configuration                                  |             | twenty two   |

| Table 5-1 Matrix processing programming interface description                                 | <u></u>     | twenty three |

| Table 5-2 Matrix processing register address description                                      | t           | wenty three  |

| Table 5-3 Explanation of the trans_ctrl register                                              | twenty four |              |

| Table 5-4 Explanations of the trans_status registers                                          | 25          |              |

| Table 6-1 Inter-processor interrupt related registers and their function descriptions         |             | <u>26</u>    |

| Table 6-2 Interrupt and communication register list of processor core 0                       | 26          |              |

| Table 6-3 List of Internuclear Interrupts and Communication Registers of No. 1 Processor Core |             | 26           |

| Table 6-4 List of Internuclear Interrupts and Communication Registers of No. 2 Processor Core |             | 27           |

| Table 6-5 List of Internuclear Interrupts and Communication Registers of Processor Core 3     | <u></u>     | 27           |

| Table 7-1 Interrupt Control Register                                                          | <u>. 29</u> |              |

| Table 7-2 IO Control Register Address 29                                                      |             |              |

| Table 7-3 Description of Interrupt Routing Register                                           | 29          |              |

| Table 7-4 Interrupt Routing Register Address 30                                               |             |              |

| Table 8-1 DDR2 SDRAM Configuration Parameter Register Format                                  |             | 33           |

| <u>Table 9-1 HyperTransport bus related pin signals</u> 76                                    |             |              |

| Table 9-2 Commands that the HyperTransport receiver can receive                               | 7           | <u>78</u>    |

| Table 9-3 Commands to be sent out in two modes                                                |             |              |

|                                                                                               |             |              |

VI

## Godson 3A1000 processor user manual table entry

| <u>Table 9-4 Addresses of the default 4 HyperTransport address windows</u>             | <u> 80</u>   |           |

|----------------------------------------------------------------------------------------|--------------|-----------|

| Table 9-5 Address window distribution of HyperTransport interface of Loongson No. 3 pr | ocessor      | 80        |

| Table 9-6 Address window provided in the HyperTransport interface of Loongson No. 3 p  | rocessor     | 81        |

| Table 9-7 All software visible registers in this module                                | 82           |           |

| Table 10-1 PCIX Controller Configuration Header                                        | 99           |           |

| Table 10-2 PCI Control Register 10                                                     | <u>0</u>     |           |

| Table 10-3 PCI / PCIX bus request and response line allocation                         | 103          |           |

| Table 10-4 LPC Controller Address Space Distribution                                   | 103          |           |

| Table 10-5 Meaning of LPC Configuration Register                                       | 104          |           |

| Table 10-6 IO Control Register                                                         | <u>. 113</u> |           |

| Table 10-7 Detailed description of registers                                           | 114          |           |

| Table 11-1 Description of Interrupt Routing Register                                   | 120          |           |

| Table 11-2 Interrupt Routing Register Address                                          | <u> 121</u>  |           |

| Table 11-3 Interrupt control bit connection and attribute configuration                | 1            | <u>22</u> |

VII

Page 13

# first part

Multi-core processor architecture, register description

1

Page 14

Godson 3A1000 Processor User Manual Part 1

## 1 Overview

## 1.1 Introduction to Loongson series processors

Loongson processor mainly includes three series. Loongson No. 1 processor and its IP series are mainly for embedded applications.

Core 2 superscalar processor and its IP series are mainly for desktop applications, and Godson 3 multi-core processor series is mainly for service

Server and high-performance machine applications. According to the needs of the application, some of Loongson 2 can also face some high-end embedded

Yes, some low-end Loongson 3 can also be used for some desktop applications. The above three series will be developed in parallel.

Loongson No. 3 multi-core series processor is based on a scalable multi-core interconnect architecture design, integrating multiple high-end on a single chip

Performance processor core and a large number of level 2 caches, and also realize the interconnection of multiple chips through high-speed I / O interface to form a larger

Modular system.

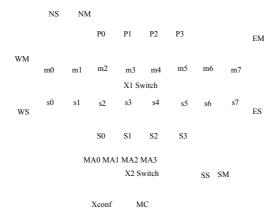

The scalable interconnection structure adopted by Loongson 3 is as follows Picture 1-1. As shown. Both the on-chip and multi-chip systems of Godson No. 3 adopt two Dimension mesh interconnection structure, where each node is composed of 8 \* 8 crossbars, each crossbar is connected to four processor cores

$And four secondary \ caches, and \ interconnect \ with \ other \ nodes \ in \ the \ four \ directions \ of \ east \ (E) \ south \ (N) \ west \ (W) \ north \ (N). \ therefore,$

2 \* 2 meshes can be connected to 16 processor cores, and 4 \* 4 meshes can be connected to 64 processor cores.

Loongson No. 3 node and two-dimensional interconnection structure, (a) node structure, (b) 2 \* 2 mesh network connected to 16 processors, (c) The 4 \* 4 mesh network connects 64 processors.

Figure 1-1 Loongson No. 3 system structure

The structure of Loongson No. 3 node is shown in Figure 1-2 below. Each node has two levels of AXI crossbars connected to the processor and two levels

$Cache, memory\ controller\ and\ IO\ controller.\ Among\ them, the\ first\ level\ AXI\ crossbar\ switch\ (called\ X1\ Switch,\ referred\ to\ as\ X1)$

Connect the processor and secondary cache. The second-level crossbar switch (called X2 Switch, referred to as X2 for short) connects the second-level cache and Memory controller.

2

#### Page 15

#### Godson 3A1000 Processor User Manual Part 1

Figure 1-2 Loongson No. 3 node structure

In each node, up to 8 \* 8 X1 crossbars are connected to four GS464 processor cores through four Master ports

(P0, P1, P2, P3 in the figure), connect four interleave secondary caches that are addressed by four slave ports

Block (S0, S1, S2, S3 in the figure), connected to the four directions of east, south, west and north through four pairs of Master / Slave

Other nodes or IO nodes (EM / ES, SM / SS, WM / WS, NM / NS in the figure).

The X2 crossbar is connected to four secondary caches through four Master ports, and one is connected to at least one Slave port

Memory controller, at least one Slave port connected to a crossbar configuration module (Xconf) is used to configure this node

The X1 and X2 address windows, etc. You can also connect more memory controllers and IO ports as needed.

The interconnection system of Loongson 3 only defines the upper layer protocol, and will not make specific provisions on the implementation of the transmission protocol,

Therefore, the interconnection between the nodes can be implemented using an on-chip network, or multiple chips can be implemented through the I/O control link and the original control

Interconnection. In a 4-node 16-core system as an example, it can be composed of 4 4-core chips or 2 8

Core chip, or based on a single chip 4 node 16 core chip. Since the physical implementation of the interconnected system is transparent to the software,

The above three configurations of the system can run the same operating system.

Loongson 3A1000 is the first product in Loongson No. 3 multi-core processor series. It is a single-node 4-core configuration.

The processor is manufactured with 65nm process and the highest working frequency is 1GHz. The main technical characteristics are as follows:

- Four 64-bit super-scalar GS464 high-performance processor cores are integrated on-chip;

- On-chip integrated 4 MB split shared secondary cache (composed of 4 individual modules, each with a capacity of 1MB);

- Maintain the cache consistency of multi-core and I / O DMA access through the directory protocol;

3

#### Page 16

#### Godson 3A1000 Processor User Manual Part 1

- Two 64-bit 400MHz DDR2 / 3 controllers are integrated on-chip;

- Two 16-bit 800MHz HyperTransport controllers are integrated on-chip;

- Each 16-bit HT port is split into two 8-way HT ports for use.

- On-chip integrated 32-bit 100MHz PCIX / 66MHz PCI;

- Integrate 1 LPC, 2 UART, 1 SPI, 16 GPIO interfaces on-chip;

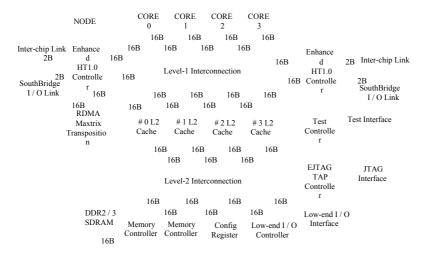

The overall architecture of Loongson 3A1000 chip is based on two-level interconnection. The structure is shown in Figure 1-3 below.

Figure 1-3 Godson 3A1000 chip structure

The first level interconnection uses a 6x6 crossbar switch, which is used to connect four CPUs (as the main device) and four second level caches

Module (as a slave), and two IO ports (each port uses a Master and a Slave). First class

Each IO port connected to the interconnect switch is connected to a 16-bit HT controller, and each 16-bit HT port can also be used as

Two 8-bit HT ports are used. The HT controller is connected to the primary interconnection switch via a DMA controller. The DMA controller

Responsible for DMA DMA control and responsible for maintaining consistency between slices. The DMA controller of Godson 3 can also be realized through configuration

Prefetch and matrix transposition or relocation.

The second level interconnection uses a 5x4 crossbar switch, connecting 4 second level cache modules (as the main device), two DDR2

Memory controller, low-speed high-speed I / O (including PCI, LPC, SPI, etc.) and the control register module inside the chip.

The above two-level interconnect switches all use separate data channels for reading and writing. The width of the data channel is 128 bits.

The processor core has the same frequency to provide high-speed on-chip data transmission.

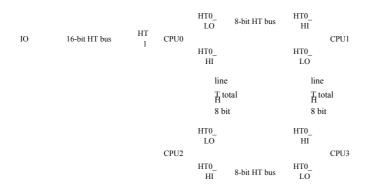

Based on Loongson No. 3 scalable interconnection architecture, 4 quad-core Loongson 3A1000 can be connected through HT port to form 4 chips 16-core SMP structure.

4

## Godson **3A1000** Processor User Manual Part 1

## 1.3 Description of Loongson 3A1000 Commercial and Industrial Chips

Loongson 3A1000 chips are available in both industrial and commercial grades. Their main features are as follows:

| Configuration                     | Commercial grade                            | Industrial grade |

|-----------------------------------|---------------------------------------------|------------------|

| Operating temperature             | $0~^{\circ}\text{C}\sim70~^{\circ}\text{C}$ | -40 °C ∼ 85 °C   |

| Whether to filter                 | _                                           | $\checkmark$     |

| Whether the quality consistency   | $\checkmark$                                |                  |

| Quality consistency test standard | GB 4937-1995                                |                  |

The Loongson 3A chip, like most semiconductor devices, has a failure rate that conforms to the bathtub curve model. Loongson 3A industrial grade chip

In order to ensure longer-term, stable, and reliable operation, and to be able to adapt to more demanding environmental temperature requirements, the chip

Reliability screening was conducted to eliminate early failure chips. This reliability screening is a 100% test, passed the screening

To meet the requirements of industrial grade chips

The main contents of the Godson 3A screening test are as follows:

| Filter items                                                                                                          | Methods and conditions (Summary)                                                     | Claim |  |  |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|-------|--|--|

| 1. Visual inspection                                                                                                  | The logo is clear, no contamination, no solder ball oxidation, and @@@chip is intact |       |  |  |

| 2. Stability baking                                                                                                   | 125 °C, 24h                                                                          | 100%  |  |  |

| 3. Rapid temperature changes                                                                                          | 10 cycles at maximum and minimum storage temperature                                 | 100%  |  |  |

| 4. Serial number                                                                                                      |                                                                                      | 100%  |  |  |

| 5. Intermediate (before aging) electrical testing 100%                                                                |                                                                                      |       |  |  |

| 6, veteran                                                                                                            | TC = 85 °C, 160h                                                                     | 100%  |  |  |

| 7. Intermediate (after aging) electrical test at room temperature 100%                                                |                                                                                      |       |  |  |

| 8. Permitted non-conforming product <b>ptp_PPM</b> ) normal temperature, when 5% < PDA≤10%, it can be All batches     |                                                                                      |       |  |  |

| Calculation Newly submitted and refined, but only allowed once                                                        |                                                                                      |       |  |  |

| 9. End point electrical test                                                                                          | Three temperature, record all test data                                              | 100%  |  |  |

| 10. External visual inspection The logo is clear, no contamination, no solder ball oxidation, and 600% chip is intact |                                                                                      |       |  |  |

5

## Page 18

Godson **3A1000** Processor User Manual Part 1

# 2 System configuration and control

## 2.1 Chip working mode

According to the structure of the system, Loongson 3A1000 has two working modes:

• Single chip mode. The system only integrates one piece of Godson 3A1000, which is a symmetric multiprocessor system (SMP).

• Multi-chip interconnect mode. The system contains 2 pieces or 4 pieces Godson 3A1000, through the HT end of Godson 3A1000

It is a non-uniform memory access multiprocessor system (CC-NUMA).

## 2.2 Description of control pins

The control pins of Loongson 3A1000 include DO\_TEST, ICCC\_EN, NODE\_ID [1: 0], CLKSEL [15: 0], PCI\_CONFIG.

Table 2-1 Control pin description

| signal         | Up and down | 1                                                  | effect                                                           |  |  |

|----------------|-------------|----------------------------------------------------|------------------------------------------------------------------|--|--|

| DO TEST        | pull up     | 1'b1 means function mode                           |                                                                  |  |  |

| DO_IEST        | pun up      | 1'b0 means test mode                               |                                                                  |  |  |

| ICCC EN        | drop down   | 1'b1 means multi-chip consistent interconnect mode |                                                                  |  |  |

| ICCC_EIV       | arop down   | 1'b0 means single chip mode                        |                                                                  |  |  |

| NODE_ID [1: 0] |             | Indicates the processor nur                        | nber in multi-chip consistent interconnect mode                  |  |  |

|                |             | Power-on clock control                             |                                                                  |  |  |

|                |             |                                                    | HT clock control                                                 |  |  |

|                |             | signal                                             | effect                                                           |  |  |

|                |             | CLKSEL [15]                                        | 1'b1 means use internal reference voltage                        |  |  |

|                |             |                                                    | 1'b0 means use external reference voltage                        |  |  |

|                |             | CLKSEL [14]                                        | 1'b1 means HT PLL uses differential clock input                  |  |  |

| CLKSEL [15: 0] | ]           |                                                    | 1'b0 means HT PLL uses normal clock input                        |  |  |

|                |             |                                                    | $2\mbox{'b00}$ means the PHY clock is $1.6\mbox{GHZ}/1$          |  |  |

|                |             | CLKSEL [13:12]  CLKSEL [11:10]                     | 2'b01 means the PHY clock is 3.2GHZ $/2$                         |  |  |

|                |             |                                                    | 2'b10 indicates that the PHY clock is a normal input clock       |  |  |

|                |             |                                                    | 2'b11 indicates that the PHY clock is a differential input clock |  |  |

|                |             |                                                    | 2'b00 means HT controller clock 200MHz                           |  |  |

|                |             |                                                    | 2'b01 means HT controller clock 400MHz                           |  |  |

|                |             |                                                    |                                                                  |  |  |

6

## Page 19

## Godson **3A1000** Processor User Manual Part 1

$2\mbox{'b}1\mbox{x}$  means that the HT controller clock is a normal input clock MEM clock control effect signal 5'b11111 means MEM clock directly uses memclk In other cases, the MEM clock is memclk \* (clksel [8: 5] +30) / (clksel [9] +3) CLKSEL [9: 5] memclk \* (clksel [8: 5] +30) must be  $600MHz \sim 1.36GHz$ memclk must be  $10 \sim 40 MHz$ CORE clock control signal effect 5'b11111 indicates that the CORE clock directly uses sysclk In other cases, the CORE clock is sysclk \* (clksel [3: 0] +30) / (clksel [4] +1) CLKSEL [4: 0] sysclk \* (clksel [3: 0] +30) must be  $600 MHz \sim 1.36 GHz$ sysclk must be 10 ~ 40MHz

```

IO configuration control

7 HT control signal pin voltage control bit 1 *

6: 5 PCIX bus speed selection *

4 PCIX bus mode selection

3 PCI master mode

2 The system starts from the PCI space

1 Use external PCI arbitration

0 HT control signal pin voltage control bit 0 *

Note*:

PCI_CONFIG [7: 0]

PCIX bus mode

0

0

PCI 33/66

0

PCI-X 66

0

PCI-X 10

PCI-X 133

HT control signal pin voltage, these signals include HT_8x2, HT_Mode,

HT_Powerok, HT_Rstn, HT_Ldt_Stopn, HT_Ldt_Reqn

0

Reserved

3.3v

```

7

## Page 20

Godson 3A1000 Processor User Manual Part 1

## 2.3 Cache consistency

Loongson 3A1000 maintains the cache consistency between the processor and the I/O accessed through the HT port by hardware, but

The hardware does not maintain the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development, and the cache consistency of I/O devices connected to the system through PCI. During driver development through PCI. During driver dr

When PCI access devices perform DMA (Direct Memory Access) transmission, the software needs to perform Cache consistency maintain.

## 2.4 Distribution of physical address space at the node level of the system

$The system physical address \ distribution \ of \ Loongson \ No. \ 3 \ series \ processors \ adopts \ a \ globally \ accessible \ hierarchical \ addressing \ design \ to \ address \ design \ to \ address \ design \ design \ to \ address \ design \ desig$

System development is compatible with expansion. The physical address width of the entire system is 48 bits. According to the upper 4 bits of the address, the entire address is empt.

Time is evenly distributed to 16 nodes, that is, each node is allocated 44-bit address space.

$Loongson\ 3A1000\ uses\ a\ single\ node\ 4\ core\ configuration, so\ Loongson\ 3A1000\ chip\ integrated\ DDR\ memory\ controller,\ HT\ and\ an analysis of the configuration of$

The corresponding addresses of the bus and PCI bus are contained in the 44-bit field from 0x0 (inclusive) to 0x1000\_0000\_0000 (not included)

In the address space, please refer to the subsequent chapters for the specific address distribution of each device.

Table 2-2 Node-level system global address distribution

|   | Node number | Address [47:44] bits | starting address | End address      |

|---|-------------|----------------------|------------------|------------------|

| ( | 0           |                      | 0x0000_0000_0000 | 0x1000_0000_0000 |

|   | 1 1         |                      | 0x1000_0000_0000 | 0x2000_0000_0000 |

| : | 2 2         |                      | 0x2000_0000_0000 | 0x3000_0000_0000 |

| 1 | 3 3         |                      | 0x3000_0000_0000 | 0x4000_0000_0000 |

| 4 | 4 4         |                      | 0x4000_0000_0000 | 0x5000_0000_0000 |

| 3 | 5 5         |                      | 0x5000_0000_0000 | 0x6000_0000_0000 |

|   | 6           |                      | 0x6000_0000_0000 | 0x7000_0000_0000 |

|   | 7 7         |                      | 0x7000_0000_0000 | 0x8000_0000_0000 |

| : | 8 8         |                      | 0x8000_0000_0000 | 0x9000_0000_0000 |

| 9  | 9   | 0x9000_0000_0000 | 0xa000_0000_0000   |

|----|-----|------------------|--------------------|

| 10 | 0xa | 0xa000_0000_0000 | 0xb000_0000_0000   |

| 11 | 0xb | 0xb000_0000_0000 | 0xc000_0000_0000   |

| 12 | 0xc | 0xc000_0000_0000 | 0xd000_0000_0000   |

| 13 | 0xd | 0xd000_0000_0000 | 0xe000_0000_0000   |

| 14 | 0xe | 0xe000_0000_0000 | 0xf000_0000_0000   |

| 15 | 0xf | 0xf000_0000_0000 | 0x1_0000_0000_0000 |

- 8

## Page 21

#### Godson 3A1000 Processor User Manual Part 1

Within each node, the 44-bit address space is further evenly distributed to a maximum of 8 devices that may be connected within the node

Prepare. Among them, the lower 43 bits of addresses are owned by 4 level 2 cache modules, and the higher 43 bits of addresses are further according to the address [43:42]

Bits are distributed to devices connected to the 4 directional ports. According to the different configuration of chip and system structure, if a port

If no slave device is connected, the corresponding address space is reserved address space, and access is not allowed.

Table 2-3 Address distribution in nodes

| device        | Address [43:41] | Start address within the | node Node end address |

|---------------|-----------------|--------------------------|-----------------------|

| Level 2 Cache | 0,1,2,3         | 0x000_0000_0000          | 0x800_0000_0000       |

| east          | 4               | 0x800_0000_0000          | 0xa00_0000_0000       |

| south         | 5               | 0xa00_0000_0000          | 0xc00_0000_0000       |

| 00            | 6               | 0xc00_0000_0000          | 0xe00_0000_0000       |

| north         | 7               | 0xe00 0000 0000          | 0x1000 0000 0000      |

For example, the base address of the east port device of node 0 is  $0x0800\_0000\_0000$ , and the base address of the east port device of node 1  $0x1800\_0000$ , and so on.

Unlike the mapping relationship of direction ports, Loongson 3A1000 can determine the second level according to the actual application access behavior

Cache cross-addressing mode. The four Level 2 Cache modules in the node correspond to a total of 43 bits of address space, and each 2

The address space corresponding to the level module is determined according to one of the two selection bits of the address bit, and can be dynamically configured by software modify. The configuration register named SCID\_SEL is set in the system to determine the address selection bits, as shown in the following table. In default

In this case, it is distributed by means of [6: 5] status hash, that is, two bits of address [6: 5] determine the corresponding level 2 cache number.

The register address is 0x3FF00400.

Table 2-4 Address distribution in nodes

| SCID_SEL | Address bit selection | SCID_SEL | Address bit selection |

|----------|-----------------------|----------|-----------------------|

| 4'h0     | 6: 5                  | 4'h8     | 23:22                 |

| 4'h1     | 9: 8                  | 4'h9     | 25:24                 |

| 4'h2     | 11:10                 | 4'ha     | 27:26                 |

| 4'h3     | 13:12                 | 4'hb     | 29:28                 |

| 4'h4     | 15:14                 | 4'hc     | 31:30                 |

| 4'h5     | 17:16                 | 4'hd     | 33:32                 |

| 4'h6     | 19:18                 | 4'he     | 35:34                 |

| 4'h7     | 21:20                 | 4'hf     | 37:36                 |

#### Page 22

#### Godson 3A1000 Processor User Manual Part 1

## 2.5 Address Routing Distribution and Configuration

The routing of Loongson 3A1000 is mainly realized through the two-stage crossbar of the system. One-level crossbar can

The master port receives requests for routing configuration. Each master port has 8 address windows, which can be completed

Target routing in 8 address windows. Each address window consists of three 64-bit registers BASE, MASK and MMAP,

BASE is aligned in K bytes; MASK adopts a format similar to the high bit of the netmask; the lower three bits of MMAP indicate the corresponding target Slave port number, MMAP [4] means to allow instruction fetch, MMAP [5] means to allow block read, MMAP [7] means window enable can.

Window hit formula: (IN ADDR & MASK) == BASE

Since Loongson 3 uses fixed routing by default, the configuration window is closed when the power is turned on.

System software is required to enable and configure it.

The address window conversion register is shown in the table below.

Table 2-5 Primary Crossbar Address Window Register Table

0x3ff0\_2000 CORE0\_WIN0\_BASE 0x3ff0\_2100 CORE1\_WIN0\_BASE 0x3ff0\_2008 CORE0\_WIN1\_BASE 0x3ff0\_2108 CORE1\_WIN1\_BASE 0x3ff0\_2010 CORE0\_WIN2\_BASE 0x3ff0\_2110 CORE1\_WIN2\_BASE 0x3ff0\_2018 CORE0\_WIN3\_BASE 0x3ff0\_2118 CORE1\_WIN3\_BASE 0x3ff0\_2020 CORE0\_WIN4\_BASE 0x3ff0\_2120 CORE1\_WIN4\_BASE 0x3ff0\_2028 CORE0\_WIN5\_BASE 0x3ff0\_2128 CORE1\_WIN5\_BASE 0x3ff0\_2030 CORE0\_WIN6\_BASE 0x3ff0\_2130 CORE1\_WIN6\_BASE 0x3ff0\_2038 CORE0\_WIN7\_BASE 0x3ff0\_2138 CORE1\_WIN7\_BASE 0x3ff0 2040 CORE0 WIN0 MASK 0x3ff0 2140 CORE1 WIN0 MASK 0x3ff0\_2048 CORE0\_WIN1\_MASK 0x3ff0\_2148 CORE1\_WIN1\_MASK 0x3ff0\_2050 CORE0\_WIN2\_MASK 0x3ff0\_2150 CORE1\_WIN2\_MASK 0x3ff0\_2058 CORE0\_WIN3\_MASK 0x3ff0\_2158 CORE1\_WIN3\_MASK 0x3ff0\_2060 CORE0\_WIN4\_MASK 0x3ff0\_2160 CORE1\_WIN4\_MASK 0x3ff0\_2068 CORE0\_WIN5\_MASK 0x3ff0\_2168 CORE1\_WIN5\_MASK 0x3ff0\_2070 CORE0\_WIN6\_MASK 0x3ff0\_2170 CORE1\_WIN6\_MASK 0x3ff0\_2078 CORE0\_WIN7\_MASK 0x3ff0\_2178 CORE1\_WIN7\_MASK 0x3ff0\_2080 CORE0\_WIN0\_MMAP 0x3ff0\_2180 CORE1\_WIN0\_MMAP 0x3ff0\_2088 CORE0\_WIN1\_MMAP 0x3ff0\_2188 CORE1\_WIN1\_MMAP 0x3ff0\_2090 CORE0\_WIN2\_MMAP 0x3ff0\_2190 CORE1\_WIN2\_MMAP 0x3ff0\_2098 CORE0\_WIN3\_MMAP 0x3ff0\_2198 CORE1\_WIN3\_MMAP

10

#### Page 23

## Godson **3A1000** Processor User Manual Part 1

0x3ff0\_20a0 CORE0\_WIN4\_MMAP 0x3ff0\_21a0 CORE1\_WIN4\_MMAP

0x3ff0\_20a8 CORE0\_WIN5\_MMAP 0x3ff0\_21a8 CORE1\_WIN5\_MMAP

0x3ff0\_20b0 CORE0\_WIN6\_MMAP 0x3ff0\_21b0 CORE1\_WIN6\_MMAP

0x3ff0\_20b8 CORE0\_WIN7\_MMAP 0x3ff0\_21b8 CORE1\_WIN7\_MMAP

0x3ff0\_2200 CORE2\_WIN0\_BASE 0x3ff0\_2300 CORE3\_WIN0\_BASE 0x3ff0\_2208 CORE2\_WIN1\_BASE 0x3ff0\_2308 CORE3\_WIN1\_BASE 0x3ff0\_2210 CORE2\_WIN2\_BASE 0x3ff0\_2310 CORE3\_WIN2\_BASE 0x3ff0 2218 CORE2 WIN3 BASE 0x3ff0 2318 CORE3 WIN3 BASE 0x3ff0\_2220 CORE2\_WIN4\_BASE 0x3ff0\_2320 CORE3\_WIN4\_BASE 0x3ff0\_2228 CORE2\_WIN5\_BASE 0x3ff0\_2328 CORE3\_WIN5\_BASE 0x3ff0 2230 CORE2 WIN6 BASE 0x3ff0 2330 CORE3 WIN6 BASE 0x3ff0\_2238 CORE2\_WIN7\_BASE 0x3ff0\_2338 CORE3\_WIN7\_BASE 0x3ff0\_2240 CORE2\_WIN0\_MASK 0x3ff0\_2340 CORE3\_WIN0\_MASK 0x3ff0\_2248 CORE2\_WIN1\_MASK 0x3ff0\_2348 CORE3\_WIN1\_MASK 0x3ff0\_2250 CORE2\_WIN2\_MASK 0x3ff0\_2350 CORE3\_WIN2\_MASK 0x3ff0\_2258 CORE2\_WIN3\_MASK 0x3ff0\_2358 CORE3\_WIN3\_MASK 0x3ff0\_2260 CORE2\_WIN4\_MASK 0x3ff0\_2360 CORE3\_WIN4\_MASK 0x3ff0\_2268 CORE2\_WIN5\_MASK 0x3ff0\_2368 CORE3\_WIN5\_MASK 0x3ff0\_2270 CORE2\_WIN6\_MASK 0x3ff0\_2370 CORE3\_WIN6\_MASK 0x3ff0\_2278 CORE2\_WIN7\_MASK 0x3ff0\_2378 CORE3\_WIN7\_MASK 0x3ff0 2280 CORE2 WINO MMAP 0x3ff0 2380 CORE3 WINO MMAP 0x3ff0\_2288 CORE2\_WIN1\_MMAP 0x3ff0\_2388 CORE3\_WIN1\_MMAP 0x3ff0 2290 CORE2 WIN2 MMAP 0x3ff0 2390 CORE3 WIN2 MMAP 0x3ff0\_2298 CORE2\_WIN3\_MMAP 0x3ff0\_2398 CORE3\_WIN3\_MMAP 0x3ff0\_22a0 CORE2\_WIN4\_MMAP 0x3ff0\_23a0 CORE3\_WIN4\_MMAP 0x3ff0\_22a8 CORE2\_WIN5\_MMAP 0x3ff0\_23a8 CORE3\_WIN5\_MMAP 0x3ff0\_22b0 CORE2\_WIN6\_MMAP 0x3ff0\_23b0 CORE3\_WIN6\_MMAP 0x3ff0\_22b8 CORE2\_WIN7\_MMAP 0x3ff0\_23b8 CORE3\_WIN7\_MMAP

0x3ff0\_2400 EAST\_WIN0\_BASE 0x3ff0\_2500 SOUTH\_WIN0\_BASE 0x3ff0\_2408 EAST\_WIN1\_BASE 0x3ff0\_2508 SOUTH\_WIN1\_BASE 0x3ff0\_2410 EAST\_WIN2\_BASE 0x3ff0\_2510 SOUTH\_WIN2\_BASE 0x3ff0\_2418 EAST\_WIN3\_BASE 0x3ff0\_2518 SOUTH\_WIN3\_BASE

11

## Page 24

#### Godson 3A1000 Processor User Manual Part 1

0x3ff0\_2420 EAST\_WIN4\_BASE 0x3ff0\_2520 SOUTH\_WIN4\_BASE

0x3ff0\_2428 EAST\_WIN5\_BASE 0x3ff0\_2528 SOUTH\_WIN5\_BASE

0x3ff0\_2430 EAST\_WIN6\_BASE 0x3ff0\_2530 SOUTH\_WIN6\_BASE

0x3ff0\_2438 EAST\_WIN7\_BASE 0x3ff0\_2538 SOUTH\_WIN7\_BASE

0x3ff0\_2440 EAST\_WIN0\_MASK 0x3ff0\_2540 SOUTH\_WIN0\_MASK

0x3ff0\_2448 EAST\_WIN1\_MASK 0x3ff0\_2548 SOUTH\_WIN1\_MASK

0x3ff0\_2445 EAST\_WIN2\_MASK 0x3ff0\_2550 SOUTH\_WIN2\_MASK

0x3ff0\_2450 EAST\_WIN3\_MASK 0x3ff0\_2558 SOUTH\_WIN3\_MASK

0x3ff0\_2458 EAST\_WIN4\_MASK 0x3ff0\_2558 SOUTH\_WIN4\_MASK

0x3ff0\_2460 EAST\_WIN5\_MASK 0x3ff0\_2560 SOUTH\_WIN5\_MASK

0x3ff0\_2460 EAST\_WIN6\_MASK 0x3ff0\_2560 SOUTH\_WIN6\_MASK

0x3ff0\_2470 EAST\_WIN6\_MASK 0x3ff0\_2570 SOUTH\_WIN6\_MASK

0x3ff0\_2478 EAST\_WIN7\_MASK 0x3ff0\_2578 SOUTH\_WIN7\_MASK

0x3ff0\_2478 EAST\_WIN0\_MMAP 0x3ff0\_2580 SOUTH\_WIN0\_MMAP

0x3ff0\_2480 EAST\_WIN1\_MMAP 0x3ff0\_2588 SOUTH\_WIN1\_MMAP

0x3ff0\_2480 EAST\_WIN2\_MMAP 0x3ff0\_2588 SOUTH\_WIN1\_MMAP

0x3ff0\_2498 EAST\_WIN3\_MMAP 0x3ff0\_2598 SOUTH\_WIN3\_MMAP

0x3ff0\_24a0 EAST\_WIN4\_MMAP 0x3ff0\_25a0 SOUTH\_WIN4\_MMAP

0x3ff0\_24a8 EAST\_WIN5\_MMAP 0x3ff0\_25a8 SOUTH\_WIN5\_MMAP

0x3ff0\_24b0 EAST\_WIN6\_MMAP 0x3ff0\_25b0 SOUTH\_WIN6\_MMAP

0x3ff0\_24b8 EAST\_WIN7\_MMAP 0x3ff0\_25b8 SOUTH\_WIN7\_MMAP

0x3ff0\_2600 WEST\_WIN0\_BASE 0x3ff0\_2700 NORTH\_WIN0\_BASE

0x3ff0\_2608 WEST\_WIN1\_BASE 0x3ff0\_2708 NORTH\_WIN1\_BASE

0x3ff0\_2610 WEST\_WIN2\_BASE 0x3ff0\_2710 NORTH\_WIN2\_BASE

0x3ff0\_2618 WEST\_WIN3\_BASE 0x3ff0\_2718 NORTH\_WIN3\_BASE

0x3ff0\_2620 WEST\_WIN4\_BASE 0x3ff0\_2720 NORTH\_WIN4\_BASE

0x3ff0\_2628 WEST\_WIN5\_BASE 0x3ff0\_2720 NORTH\_WIN5\_BASE

0x3ff0\_2630 WEST\_WIN6\_BASE 0x3ff0\_2730 NORTH\_WIN6\_BASE

0x3ff0\_2630 WEST\_WIN6\_BASE 0x3ff0\_2730 NORTH\_WIN7\_BASE

0x3ff0\_2638 WEST\_WIN7\_BASE 0x3ff0\_2730 NORTH\_WIN7\_BASE

0x3ff0\_2640 WEST\_WIN0\_MASK 0x3ff0\_2740 NORTH\_WIN0\_MASK

0x3ff0\_2640 WEST\_WIN1\_MASK 0x3ff0\_2740 NORTH\_WIN1\_MASK

0x3ff0\_2650 WEST\_WIN3\_MASK 0x3ff0\_2750 NORTH\_WIN3\_MASK

0x3ff0\_2650 WEST\_WIN3\_MASK 0x3ff0\_2758 NORTH\_WIN3\_MASK

0x3ff0\_2660 WEST\_WIN4\_MASK 0x3ff0\_2760 NORTH\_WIN4\_MASK

12

#### Page 25

#### Godson 3A1000 Processor User Manual Part 1

0x3ff0\_2668 WEST\_WIN5\_MASK 0x3ff0\_2770 NORTH\_WIN5\_MASK 0x3ff0\_2670 WEST\_WIN6\_MASK 0x3ff0\_2770 NORTH\_WIN6\_MASK 0x3ff0\_2678 WEST\_WIN7\_MASK 0x3ff0\_2778 NORTH\_WIN7\_MASK 0x3ff0\_2680 WEST\_WIN0\_MMAP 0x3ff0\_2780 NORTH\_WIN0\_MMAP 0x3ff0\_2688 WEST\_WIN1\_MMAP 0x3ff0\_2780 NORTH\_WIN1\_MMAP 0x3ff0\_2690 WEST\_WIN2\_MMAP 0x3ff0\_2790 NORTH\_WIN2\_MMAP 0x3ff0\_2690 WEST\_WIN3\_MMAP 0x3ff0\_2790 NORTH\_WIN3\_MMAP 0x3ff0\_26a0 WEST\_WIN4\_MMAP 0x3ff0\_27a0 NORTH\_WIN4\_MMAP 0x3ff0\_26a8 WEST\_WIN5\_MMAP 0x3ff0\_27a0 NORTH\_WIN5\_MMAP 0x3ff0\_26a0 WEST\_WIN6\_MMAP 0x3ff0\_27a0 NORTH\_WIN6\_MMAP 0x3ff0\_26b0 WEST\_WIN6\_MMAP 0x3ff0\_27b0 NORTH\_WIN6\_MMAP 0x3ff0\_26b0 WEST\_WIN7\_MMAP 0x3ff0\_27b0 NORTH\_WIN7\_MMAP

In the second-level XBAR of Godson 3, there are CPU address space (including HT space), DDR2 address space, and PCI

The address space has three IP-related address spaces. The address window is for CPU and PCI-DMA with two Master functions

$IP\ is\ set\ for\ routing\ and\ address\ translation.\ Both\ CPU\ and\ PCI-DMA\ have\ 8\ address\ windows,\ you\ can\ finish$

The selection of the target address space and the conversion from the source address space to the target address space. Each address window consists of BASE,

$MASK\ and\ MMAP\ are\ composed\ of\ three\ 64-bit\ registers,\ BASE\ is\ aligned\ with\ K\ bytes,\ and\ MASK\ adopts\ a\ similar\ netmask\ high\ bit\ as\ 1.$

, The lower three digits of MMAP are routing.

At level 2 XBAR, the correspondence between the label and the module is as follows: the number corresponding to the new address space (two of which The number of each DDR2 is 0 and 1, the PCI / Local IO number is 2, and the configuration register module is connected to port 3).

Table 2-6 Correspondence between the labels and the modules at level 2 XBAR

| Label | Default value                    |

|-------|----------------------------------|

| 0     | No. 0 DDR2 / 3 controller        |

| 1     | No. 1 DDR2 / 3 controller        |

| 2     | Low-speed I / O (PCI, LPC, etc.) |

#### 3 Configuration register

As shown in the table below. MMAP [4] means to allow instruction fetch, MMAP [5] means to allow block read, MMAP [7] means to use window

can.

Table 2-7 The space access attributes corresponding to the MMAP field

[4] [5] [7]

Allow fetching Block read Window enable

Compared with the address configuration of the first-level XBAR, the address configuration of the second-level XBAR adds the function of address translation. In contrast

Next, the window configuration of the first-level XBAR cannot perform address translation for Cache consistency requests, otherwise it is in the second-level cache

Will be inconsistent with the address of the first-level cache of the processor, resulting in incorrect maintenance of Cache consistency.

13

## Page 26

#### Godson 3A1000 Processor User Manual Part 1

Window hit formula: (IN\_ADDR & MASK) == BASE

New address conversion formula: OUT\_ADDR = (IN\_ADDR & ~ MASK) | {MMAP [63:10], 10'h0}

The address window conversion register is as follows.

Table 2-8 Secondary XBAR address window conversion register table

| address register       | description                       | Default value         |

|------------------------|-----------------------------------|-----------------------|

| 3ff0 0000 CPU_WIN0_BAS | SE CPU window 0 base address 0x0  |                       |

| 3ff0 0008 CPU_WIN1_BAS | SE CPU window 1 base address 0x10 | 00_0000               |

| 3ff0 0010 CPU_WIN2_BAS | SE CPU window 2 base address 0x0  |                       |

| 3ff0 0018 CPU_WIN3_BAS | SE CPU window 3 base address 0x0  |                       |

| 3ff0 0020 CPU_WIN4_BAS | SE CPU window 4 base address 0x0  |                       |

| 3ff0 0028 CPU_WIN5_BAS | SE CPU window 5 base address 0x0  |                       |

| 3ff0 0030 CPU_WIN6_BAS | SE CPU window 6 base address 0x0  |                       |

| 3ff0 0038 CPU_WIN7_BAS | SE CPU window 7 base address 0x0  |                       |

| 3ff0 0040 CPU_WIN0_MAS | SK CPU window 0 mask              | 0xffff_ffff_f000_0000 |

| 3ff0 0048 CPU_WIN1_MAS | SK CPU window 1 mask              | 0xffff_ffff_f000_0000 |

| 3ff0 0050 CPU_WIN2_MAS | SK CPU window 2 mask              | 0x0                   |

| 3ff0 0058 CPU_WIN3_MAS | SK CPU window 3 mask              | 0x0                   |

| 3ff0 0060 CPU_WIN4_MAS | SK CPU window 4 mask              | 0x0                   |

| 3ff0 0068 CPU_WIN5_MAS | SK Mask of CPU window 5           | 0x0                   |

| 3ff0 0070 CPU_WIN6_MAS | SK CPU window 6 mask              | 0x0                   |

| 3ff0 0078 CPU_WIN7_MAS | SK CPU window 7 mask              | 0x0                   |

| 3ff0 0080 CPU_WIN0_MM  | AP CPU window 0 new base address  | 0xf0                  |

| 3ff0 0088 CPU_WIN1_MM  | AP CPU window 1 new base address  | 0x1000_00f2           |

| 3ff0 0090 CPU_WIN2_MM  | AP CPU window 2 new base address  | 0                     |

| 3ff0 0098 CPU_WIN3_MM  | AP CPU window 3 new base address  | 0                     |

| 3ff0 00a0 CPU_WIN4_MM. | AP CPU window 4 new base address  | 0x0                   |

| 3ff0 00a8 CPU_WIN5_MM  | AP CPU window 5 new base address  | 0x0                   |

| 3ff0 00b0 CPU_WIN6_MM  | AP CPU window 6 new base address  | 0                     |

| 3ff0 00b8 CPU_WIN7_MM  | AP CPU window 7 new base address  | 0                     |

#### Page 27

#### Godson 3A1000 Processor User Manual Part 1

3ff0 0100 PCI\_WIN0\_BASE PCI window 0 base address 0x8000\_0000 3ff0 0108 PCI\_WIN1\_BASE PCI window 1 base address 0x0 3ff0 0110 PCI\_WIN2\_BASE PCI window 2 base address 0x0 3ff0 0118 PCI\_WIN3\_BASE PCI window 3 base address 0x0 3ff0 0120 PCI\_WIN4\_BASE PCI window 4 base address 0x0 3ff0 0128 PCI\_WIN5\_BASE PCI window 5 base address 0x0 3ff0 0130 PCI\_WIN6\_BASE PCI window 6 base address 0x0 3ff0 0138 PCI\_WIN7\_BASE PCI window 7 base address 0x0 3ff0 0140 PCI\_WIN0\_MASK PCI window 0 mask 0xffff\_ffff\_8000\_0000 3ff0 0148 PCI\_WIN1\_MASK Mask of PCI window 1 0x03ff0 0150 PCI\_WIN2\_MASK PCI window 2 mask 0x0 3ff0 0158 PCI\_WIN3\_MASK PCI window 3 mask 0x03ff0 0160 PCI\_WIN4\_MASK PCI window 4 mask 0x03ff0 0168 PCI\_WIN5\_MASK PCI window 5 mask 0x0 3ff0 0170 PCI\_WIN6\_MASK Mask of PCI window 6 0x03ff0 0178 PCI WIN7 MASK Mask of PCI window 7 0x03ff0 0180 PCI\_WIN0\_MMAP PCI window 0 new base address 0xf0 3ff0 0188 PCI\_WIN1\_MMAP PCI window 1 new base address 0x0 3ff0 0190 PCI WIN2 MMAP New base address of PCI window 2 0 3ff0 0198 PCI\_WIN3\_MMAP PCI window 3 new base address 0 3ff0 01a0 PCI\_WIN4\_MMAP PCI window 4 new base address 0x0 3ff0 01a8 PCI\_WIN5\_MMAP PCI window 5 new base address 0x0 3ff0 01b0 PCI\_WIN6\_MMAP New base address of PCI window 6 0 3ff0 01b8 PCI\_WIN7\_MMAP PCI window 7 new base address 0

$According \ to \ the \ default \ register \ configuration, \ after \ the \ chip \ is \ started, \ the \ address \ range \ of \ 0x00000000-0x0fffffff \ of \ the \ CPU$

-The address range (256M) of 0x8fffffff is mapped to the address range of 0x00000000-0x0fffffff of DDR2.

The software can implement new address space routing and conversion by modifying the corresponding configuration registers.

In addition, when there is a read access to an illegal address due to CPU speculative execution, none of the eight address windows hit.

15

## Page 28

## Godson **3A1000** Processor User Manual Part 1

The configuration register module returns all 0 data to the CPU to prevent the CPU from dying.

Base address

Table 2-9 Secondary XBAR default address configuration

Tuole 2 / Secondary TES. In default address configuration

High position

0x0000\_0000\_1000\_0000

0x0000\_0000\_2000\_0000

Low-speed I / O (PCI, etc.)

# 2.6 Chip configuration and sampling register

$The \ chip\ configuration\ register\ (Chip\_config)\ and\ chip\ sampling\ register\ (chip\_sample)\ in\ Godson\ 3\ provide$

A mechanism to read and write the configuration of the chip.

Table 2-10 Chip Configuration Register (Physical Address 0x1fe00180)

| Bit field      | Field name | access | Reset value | description                                                       |

|----------------|------------|--------|-------------|-------------------------------------------------------------------|

| Freq_scal      | le_ctrl    | RW     | 3'b111      | Processor core frequency division                                 |

| 2: 0           |            |        |             | The actual frequency of the processor core is                     |

|                |            |        |             | PLL frequency * (Freq_scal_ctrl + 1) / 8                          |

|                |            |        |             | Whether to use software to configure DDR frequency multiplication |

| 3 DDR_Clksel_  | en         | RW     | 1'b0        | 1: Use software configuration                                     |

|                |            |        |             | 0: use pin CLKSEL configuration                                   |

|                |            |        |             | Whether to disable the DDR configuration space                    |

| 8 Disable_ddr2 | _confspace | RW     | 1'b0        | 1: Disabled                                                       |

|                |            |        |             | 0: Do not disable                                                 |

|                |            |        |             | Whether to open DDR read access buffer                            |

| 9 DDR_buffer_  | cpu        | RW     | 1'b0        | 1: open                                                           |

|                |            |        |             | 0: disabled                                                       |

|                |            |        |             | Whether to enable processor core 0                                |

| 12 Core0_en    |            | RW     | 1'b1        | 1: open                                                           |

|                |            |        |             | 0: disabled                                                       |

|                |            |        |             | Whether to enable processor core 1                                |

| 13 Core1_en    |            | RW     | 1'b1        | 1: open                                                           |

|                |            |        |             | 0: disabled                                                       |

|                |            |        |             | Whether to enable processor core 2                                |

| 14 Core2_en    |            | RW     | 1'b1        | 1: open                                                           |

|                |            |        |             | 0: disabled                                                       |

|                |            |        |             | Whether to enable processor core 3                                |

| 15 Core3_en    |            | RW     | 1'b1        | 1: open                                                           |

|                |            |        |             | 0: disabled                                                       |

| 16 Ma0 av      |            | DW     | 1%1         | Whether to enable DDR controller 0                                |

| 16 Mc0_en      |            | RW     | 1'b1        | 1: open                                                           |

|                |            |        |             |                                                                   |

16

# Page 29

## Godson **3A1000** Processor User Manual Part 1

|                  |    |          | 0: disabled                                                    |

|------------------|----|----------|----------------------------------------------------------------|

|                  |    |          | Whether to enable DDR controller 1                             |

| 17 Mcl_en        | RW | 1'b1     | 1: open                                                        |

|                  |    |          | 0: disabled                                                    |

|                  |    |          | Software reset DDR controller 0                                |

| 18 DDR_reset0    | RW | 1'b1     | 1: Reset                                                       |

|                  |    |          | 0: Unreset                                                     |

|                  | RW |          | Software reset DDR controller 1                                |

| 19 DDR_reset1    |    | 1'b1     | 1: Reset                                                       |

|                  |    |          | 0: Unreset                                                     |

|                  | RW | 1'b1     | Whether to enable the HT controller 0                          |

| 22 HT0_en        |    |          | 1: open                                                        |

|                  |    |          | 0: disabled                                                    |

|                  | RW | 1'b1     | Whether to enable the HT controller 1                          |

| 23 HT1_en        |    |          | 1: open                                                        |

|                  |    |          | 0: disabled                                                    |

| 20:24 DDD - Cll1 | RW | 5'b11111 | Software configuration DDR clock multiplier relationship (when |

| 28:24 DDR_Clksel |    |          | (Valid when DDR_Clksel_en is 1)                                |

| C - J   | 211000  | Processor | II   | M      | ı |

|---------|---------|-----------|------|--------|---|

| เรดสรดท | 3A LUUU | Processor | Hser | Maniia | ı |

|       | HT_freq_scale_ctrl0  | RW | 3'b111 | HT controller divide by 0                                   |

|-------|----------------------|----|--------|-------------------------------------------------------------|

| 21.20 |                      |    |        | The actual frequency of the controller is                   |

| 31:29 |                      |    |        | HT controller frequency *                                   |

|       |                      |    |        | (HTFreq_scal_ctrl + 1) / 8                                  |

|       | HT_freq_scale_ctrl0  | RW | 3'b111 | HT controller divided by 1                                  |

|       |                      |    |        | The actual frequency of the controller is                   |

| 34:32 |                      |    |        | HT controller frequency *                                   |

|       |                      |    |        | (HTFreq_scal_ctrl + 1) / 8                                  |

|       | Mc0_prefetch_disable | RW | 1'b0   | Whether to disable MC0 prefetch function (for different     |

|       |                      |    |        | Program behavior will produce different performance effects |

| 35    |                      |    |        | ring)                                                       |

|       |                      |    |        | 1: Disabled                                                 |

|       |                      |    |        | 0: Do not disable                                           |

|       | Mc1_prefetch_disable | RW | 1'b0   | Whether to disable MC1 prefetch function (for different     |

|       |                      |    |        | Program behavior will produce different performance effects |

| 36    |                      |    |        | ring)                                                       |

|       |                      |    |        | 1: Disabled                                                 |

|       |                      |    |        | 0: Do not disable                                           |

| other |                      | R  |        | Keep                                                        |

|       |                      |    |        |                                                             |

Table 2-11 Chip sampling register (physical address 0x1fe00190)

| Bit field         | Field name | access | Reset value |                | description |

|-------------------|------------|--------|-------------|----------------|-------------|

| 15: 0 Pad2v5_ctrl |            | RW     | 16'h780     | 2v5pad control |             |

| 31:16 Pad3v3_ctrl |            | RW     | 16'h780     | 3v3pad control |             |

17

## Page 30

## Godson **3A1000** Processor User Manual Part 1

| 47:32 Sys_clksel     | R | Onboard frequency setting                                     |

|----------------------|---|---------------------------------------------------------------|

|                      |   | Indicates whether the processor core is unavailable, each bit |

| 61 (0 P. 1)          |   | Do not correspond to processor core 3-processor core 0        |

| 51:48 Bad_ip_core    | R | 0-available                                                   |

|                      |   | 1-not available                                               |

| 53:52 Bad_ip_ddr     | R | Whether 2 DDR controllers are bad                             |

| 57:56 Bad_ip_ht      | R | Whether 2 HT controllers are bad                              |

|                      |   | Temperature sensor 0 temperature, used to monitor secondary   |

|                      | _ | Temperature near the buffer, accuracy is +/- 6                |

| 102: 96 Thsens0_out  | R | Fahrenheit (Note: The sensor sometimes has abnormalities      |

|                      |   | temperature)                                                  |

|                      |   | Temperature sensor 0 temperature overflow (over 128           |

| 103 Thsens0_overflow | R | degree)                                                       |

|                      |   | Temperature sensor 1 temperature for monitoring processing    |

| 110: 104 Thsens1_out | R | The temperature near the core, the accuracy is +/- 6          |

|                      |   | Degree                                                        |

|                      | _ | Temperature sensor 1 temperature overflow (over 128           |

| 111 Thsens1_overflow | R | degree)                                                       |

| other                | R | Keep                                                          |

18

## Page 31

#### Godson 3A1000 Processor User Manual Part 1

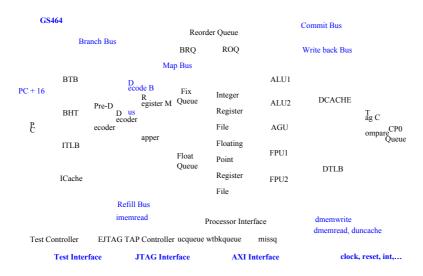

## 3 GS464 processor core

GS464 is a four-launch 64-bit high-performance processor core. The processor core can be used as a single core for high-end embedded

Applications and desktop applications can also be used as basic processor cores to form on-chip multi-core systems for server and high-performance applications use. Multiple GS464 cores in Loongson 3A1000 and the secondary cache module form one through the AXI interconnection network

Multi-core structure of distributed shared secondary cache. The main features of GS464 are as follows:

- MIPS64 compatible, support Godson extended instruction set;

- Four-shot superscalar structure, two fixed-point, two floating-point, and one memory access component;

- Each floating-point component supports full-pipe 64-bit / dual 32-bit floating-point multiply-add operations;

- · The memory access component supports 128-bit memory access, and the virtual address and physical address are 48 bits each;

- Support register renaming, dynamic scheduling, branch prediction and other out-of-order execution technologies;

- 64 fully linked TLBs, independent 16 instruction TLBs, variable page size;

- The size of the first-level instruction cache and data cache are 64KB, and the 4-way group is connected;

- Support Non-blocking access and Load-Speculation and other access optimization technologies;

- Support Cache consistency protocol, can be used for on-chip multi-core processor;

- Instruction Cache implements parity check, and Data Cache implements ECC check;

- Support the standard EJTAG debugging standard, which is convenient for hardware and software debugging;

- Standard 128-bit AXI interface.

The structure of GS464 is shown in the figure below. For more detailed introduction, please refer to GS464 user manual and MIPS64 User manual.

## Page 32

## Godson **3A1000** Processor User Manual Part 1

Figure 3-1 GS464 structure diagram

20

## Page 33

Godson  ${\bf 3A1000}$  Processor User Manual Part 1

# 4 Secondary Cache

Make GS464 the processor IP including secondary cache; you can also connect multiple GS464 through AXI network and

Multiple secondary cache modules form an on-chip multi-processor CMP structure. The main features of the secondary cache module include:

- Using 128-bit AXI interface.

- 8 items Cache access queue.

- Keywords first.

- The fastest read is 8 beats from receiving a read invalid request to returning data

- Support Cache consistency protocol through the directory.

- It can be used for on-chip multi-core structure, and can also be directly connected with single processor IP.

- The soft IP level can be configured with the size of the secondary cache (512KB / 1MB).

- The four-way group connection structure is adopted.

- It can be closed dynamically during operation.

- Support ECC check.

- Support DMA consistent read and write and prefetch reading.

- Support 16 kinds of second-level cache hashes.

- Support to lock secondary cache by window.

- Ensure that read data returns atomicity.