Volume II

GS464E processor core V1.03

2016 Nian 6 Yue

Loongson Zhongke Technology Co., Ltd.

# Copyright Notice

The copyright of this document belongs to Loongson Zhongke Technology Co., Ltd. and reserves all rights. Without written permission, no company or individual shall Any part of the file is open, reprinted or otherwise distributed to third parties. Otherwise, it will be held accountable.

# Disclaimer

This document only provides periodic information, and the content can be updated at any time according to the actual situation of the product without notice. If due to improper use of docume The company does not assume any responsibility for the direct or indirect losses caused.

## Loongson Zhongke Technology Co., Ltd.

Loongson Technology Corporation Limited Address: Building 2, Longxin Industrial Park, Zhongguancun Environmental Protection Technology Demonstration Park, Haidian District, Beijing Building No. 2, Loongson Industrial Park, Zhongguancun Environmental Protection Park, Haidian District, Beijing Telephone (Tel): 010-62546668 Fax: 010-62600826

Page 3

Godson 3A2000 / 3B2000 Processor User Manual • Next

# Reading guide

"Godson 3A2000 / 3B2000 Processor User Manual" is divided into two volumes. Volume 2 of the "Loongson 3A2000 / 3B2000 Processor User Manual" introduces Loongson 3A2000 / 3B2000 processing in detail from the perspective of system software developers The GS464E high-performance processor core used in the processor.

Introduction to the meaning of special formats

1. In this document, the description of a certain field of the CP0 control register is in the format of Reg.Field, where Reg is the help of the control register. Notation, Field is the mnemonic of the field to be described in this register. For example, EBase.CPUNum represents the CPUNum of the EBase control register area.

2. The description of the data content interception part in this document adopts the format of [m: n] or m.n, which means that the content from the nth to the mth is selected

Bit. m and n take values from 0,  $m \ge n$ .

# Page 4

# Godson 3A2000 / 3B2000 Processor User Manual • Next

# Version history

| Document update record |                | Godson 3A2000 / 3B2000 Processor User Manual |  |

|------------------------|----------------|----------------------------------------------|--|

|                        | Document name: | Volume II                                    |  |

|                        | version number | V1.03                                        |  |

|                        | founder:       | R & D Center Chip R & D Department           |  |

|                        | Creation Date: | 2017-04-07                                   |  |

# Update history

| Serial nu | mbepdated  | updater version nu         | mber update content                                                                                                                                                                                                                                                                                         |

|-----------|------------|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1         | 2016/03/01 | Chip R & D Departmento     | The first draft is completed.                                                                                                                                                                                                                                                                               |

| 2         | 2016/03/29 | Chip R & D Department V1.0 | <ol> <li>Update the definition of bit 8 of the GSCONFIG register, see section 7.34.</li> <li>Added section 2.4.12, about the compatibility of DI and EI instructions.</li> </ol>                                                                                                                            |

| 3         | 2016/06/08 | Chip R & D Department V1.0 | 2 Update 2. Overview of Instruction Set                                                                                                                                                                                                                                                                     |

| 4         | 2017/04/07 | Chip R & D Department V1.0 | <ol> <li>Delete some inaccurate performance count events in section 8.2.1 and adjust the partiality         A description that can count events.</li> <li>2. The description of the SYNC instruction in Section 2.4.6.</li> <li>3. Adjust the description of SYNCI instruction in section 2.4.7.</li> </ol> |

Manual information feedback: <a href="mailto:service@loongson.cn">service@loongson.cn</a>

You can also use the problem feedback website <u>http://bugs.loongnix.org/</u>Submit the problems in the use of chip products to our company and obtain Get technical support.

Page 5

## Godson 3A2000 / 3B2000 Processor User Manual • Next

# table of Contents

|            |                  | overview                                                       |       |

|------------|------------------|----------------------------------------------------------------|-------|

| <u>2.1</u> |                  | PS64 compatible general instruction list                       |       |

|            | <u>2.1.1</u>     | Fetch instruction                                              |       |

|            | <u>2.1.2</u>     | Operation instruction                                          |       |

|            | <u>2.1.3</u>     | Jump and branch instructions                                   |       |

|            | <u>2.1.4</u>     | Coprocessor 0 instruction                                      |       |

|            | <u>2.1.5</u>     | Other commands                                                 |       |

| <u>2.2</u> | <u>Ov</u>        | erview of MIPS64 compatible floating point instruction set     | <br>8 |

|            | <u>2.2.1</u>     | FPU data type                                                  |       |

|            | <u>2.2.2</u>     | Floating-point registers                                       |       |

|            | <u>2.2.3</u>     | Floating Point Control Register                                |       |

|            | <u>2.2.4</u>     | Floating point exception                                       |       |

|            | <u>2.2.5</u>     | MIPS64 compatible floating point instruction list              |       |

| <u>2.3</u> | <u>MI</u>        | PS64 DSP instruction set overview                              |       |

|            | <u>2.3.1</u>     | MIPS64 DSP ASE compatible instruction list                     |       |

|            | <u>2.3.2</u>     | Supplementary instructions to the MIPS DSP instruction manual  |       |

| <u>2.4</u> | MI               | PS64 compatible instruction implementation related definitions | <br>  |

|            | <u>2.4.1</u>     | The load instruction targeted at general register 0            |       |

|            | <u>2.4.2</u>     | PREF command                                                   |       |

|            | <u>2.4.3</u>     | RDHWR instruction                                              |       |

|            | <u>2.4.4</u>     | PREFX instruction                                              |       |

|            | <u>2.4.5</u>     | WAIT instruction                                               |       |

|            | <u>2.4.6</u>     | SYNC command                                                   |       |

|            | <u>2.4.7</u>     | SYNCI command                                                  |       |

|            | <u>2.4.8</u>     | TLBINV and TLBINVF instructions                                |       |

|            | <u>2.4.9</u>     | CACHE instruction                                              |       |

|            | <u>2.4.10 M</u>  | ADD.fmt, MSUB.fmt, NMADD.fmt, NMSUB.fmt instructions           |       |

|            | <u>2.4.11 EF</u> | IB, SSNOP instructions                                         |       |

|            | <u>2.4.12 DI</u> | and EI instructions                                            |       |

| 2.5        | Go               | dson extended instruction set                                  |       |

| Proc       | essor opera      | ting mode                                                      |       |

| <u>3.1</u> |                  | inition of processor operating mode                            |       |

|            | 3.1.1            | Debug mode                                                     |       |

|            | 3.1.2            | Root-Core Mode                                                 |       |

|            |                  |                                                                |       |

<u>4.1</u>

Ι

# Page 6

|          |                   |                       | Godson 3A2000 / 3B2000 Processor                                                                | r User Manual • Next         |            |

|----------|-------------------|-----------------------|-------------------------------------------------------------------------------------------------|------------------------------|------------|

|          |                   | <u>4.1.4</u>          | Mapped Address and Unmapped Address                                                             |                              |            |

|          | <u>4.2</u>        | 1                     | Host virtual address space                                                                      |                              |            |

|          |                   | <u>4.2.1</u>          | Host address space division and access control                                                  |                              |            |

|          |                   | <u>4.2.2</u>          | Host address space kseg0 segment and kseg1 segment address translation, cacheability and        | cache consistency attributes |            |

|          |                   | <u>4.2.3</u>          | Address translation, cacheability and cache coherence attributes of the host address space xl   | <u>kphys 43</u>              |            |

|          |                   | <u>4.2.4</u>          | Address translation of the kuseg segment of the host address space when Status. $ERL = 1 \dots$ |                              |            |

|          |                   | <u>4.2.5</u>          | <u>Special processing of kseg3 segment of host address space when Debug.DM = 1</u>              |                              | <u> 43</u> |

|          |                   | <u>4.2.6</u>          | Special processing of data access virtual address when Status.UX = 0 in user mode               |                              |            |

|          | <u>4.3</u>        | -                     | ILB-based virtual and real address mapping                                                      |                              |            |

|          |                   | <u>4.3.1</u>          | TLB hierarchy                                                                                   |                              |            |

|          |                   | <u>4.3.2</u>          | JTLB Organizational Structure                                                                   |                              |            |

|          |                   | <u>4.3.3</u>          | JTLB table entry                                                                                |                              |            |

|          |                   | <u>4.3.4</u>          | TLB Software Management                                                                         |                              |            |

|          |                   | <u>4.3.5</u>          | TLB initialization and emptying                                                                 |                              |            |

|          |                   | <u>4.3.6</u>          | TLB-based virtual and real address translation process                                          |                              |            |

| <u>5</u> |                   |                       | ization and management                                                                          |                              |            |

|          | <u>5.1</u>        |                       | Processor storage hierarchy and cache organization structure at all levels                      |                              | <u>53</u>  |

|          |                   | <u>5.1.1</u>          | Processor storage hierarchy                                                                     |                              |            |

|          |                   | <u>5.1.2</u>          | First-level instruction cache (I-Cache)                                                         |                              |            |

|          |                   | <u>5.1.3</u>          | D-Cache                                                                                         |                              |            |

|          |                   | <u>5.1.4</u>          | V-Cache                                                                                         |                              |            |

|          |                   | <u>5.1.5</u>          | Three-level shared cache (S-Cache)                                                              |                              |            |

|          | <u>5.2</u>        |                       | Cache algorithm and cache consistent properties                                                 |                              |            |

|          |                   | <u>5.2.1</u><br>5.2.2 |                                                                                                 |                              |            |

|          |                   | <u>5.2.2</u><br>5.2.3 | Consistent cache algorithm                                                                      |                              |            |

|          | <u>5.3</u>        |                       |                                                                                                 |                              |            |

|          | <u>5.5</u><br>5.4 |                       | Cache management                                                                                |                              |            |

|          | <u></u>           | 5.4.1                 | CACHE instruction                                                                               |                              |            |

|          |                   | 5.4.2                 | Cache initialization                                                                            |                              |            |

|          |                   | 5.4.3                 | Consistency maintenance between first-level instruction cache and first-level data cache        |                              | 63         |

|          |                   | 5.4.4                 | Cache consistency maintenance between processor and DMA device                                  |                              |            |

|          |                   | 5.4.5                 | Cache alias and page coloring                                                                   |                              |            |

| <u>6</u> | Proc              | cessor ex             | ceptions and interrupts                                                                         |                              |            |

|          | <u>6.1</u>        | 1                     | Processor exception                                                                             |                              |            |

|          |                   | <u>6.1.1</u>          | Exception priority                                                                              | <u></u>                      |            |

|          |                   | <u>6.1.2</u>          | Exceptional entry vector position                                                               |                              |            |

|          |                   | <u>6.1.3</u>          | General processing of processor hardware response exceptions                                    |                              |            |

|          |                   | <u>6.1.4</u>          | Cold reset exception                                                                            |                              |            |

|          |                   | <u>6.1.5</u>          | Non-maskable interrupt                                                                          |                              |            |

|          |                   | <u>6.1.6</u>          | Interruption exception                                                                          |                              |            |

|          |                   | <u>6.1.7</u>          | Exception for wrong address                                                                     |                              |            |

|          |                   | <u>6.1.8</u>          | TLB refill exception                                                                            |                              |            |

Π

Godson 3A2000 / 3B2000 Processor User Manual • Next

| <u>6.1.9</u>  | XTLB refill exception                                            |  |

|---------------|------------------------------------------------------------------|--|

| <u>6.1.10</u> | TLB invalid exception                                            |  |

| 6.1.11        | TLB modification exception                                       |  |

| 6.1.12        | TLB execution blocking exception                                 |  |

|               | TLB read block exception                                         |  |

|               | Cache error exception                                            |  |

|               | Integer overflow exception                                       |  |

| 6.1.16        | Trap exception                                                   |  |

| 6.1.17        | System call exception                                            |  |

| 6.1.18        | Breakpoint exceptions                                            |  |

|               | Exception to reserved instructions                               |  |

|               | Coprocessor unavailable exception                                |  |

|               | Floating point exception                                         |  |

| 6.1.22        | Exception of floating point stack                                |  |

| _             | nterruption                                                      |  |

| 6.2.1         | Necessary conditions for interrupt response                      |  |

| 6.2.2         | Interrupt mode                                                   |  |

| 6.2.3         | Supplementary explanation of interrupt handling                  |  |

|               | 0 Register                                                       |  |

|               | Root coprocessor 0 register overview                             |  |

|               | ndex register (CP0 Register 0, Select 0)                         |  |

|               | Random register (CP0 Register 1, Select 0)                       |  |

|               | EntryLo0 and EntryLo1 registers (CP0 Register 2 and 3, Select 0) |  |

|               | Context register (CP0 Register 4, Select 0)                      |  |

|               | JserLocal register (CP0 Register 4, Selelct 2)                   |  |

|               | ageMask Register (CP0 Register 5, Select 0)                      |  |

|               | PageGrain Register (CP0 Register 5, Select 1)                    |  |

|               | WBase register (CP0 Register 5, Select 5)                        |  |

|               | PWField register (CP0 Register 5, Select 6)                      |  |

|               | WSize register (CP0 Register 5, Select 6)                        |  |

|               | Vired register (CP0 Register 6, Select 0)                        |  |

|               | WCtl register (CP0 Register 6, Select 6)                         |  |

|               | IWREna register (CP0 Register 7, Select 0)                       |  |

|               | BadVAddr register (CP0 Register 8, Select 0)                     |  |

|               | Count register (CP0 Register 9, Select 0)                        |  |

|               | SEBase register (CP0 Register 9, Select 6)                       |  |

|               | PGD Register (CP0 Register 9, Select 7)                          |  |

|               | EntryHi register (CP0 Register 10, Select 0)                     |  |

|               | Compare register (CPO Register 11, Select 0)                     |  |

|               | Status register (CP0 Register 12, Select 0)                      |  |

|               | ntCtl register (CP0 Register 12, Select 1)                       |  |

|               | RSCtl register (CP0 Register 12, Select 2)                       |  |

|               | Cause register (CP0 Register 13, Select 0)                       |  |

III

<u>7</u>

Page 8

Godson 3A2000 / 3B2000 Processor User Manual  ${\scriptstyle \bullet}$  Next

| <u>7.25</u> | EPC register (CP0 Register 14, Select 0)      |  |

|-------------|-----------------------------------------------|--|

| <u>7.26</u> | PRId register (CP0 Register 15, Select 0)     |  |

| <u>7.27</u> | EBase register (CP0 Register 15, Select 1)    |  |

| <u>7.28</u> | Config register (CP0 Register 16, Select 0)   |  |

| <u>7.29</u> | Config1 register (CP0 Register 16, Select 1)  |  |

| <u>7.30</u> | Config2 register (CP0 Register 16, Select 2)  |  |

| <u>7.31</u> | Config3 register (CP0 Register 16, Select 3)  |  |

| <u>7.32</u> | Config4 register (CP0 Register 16, Select 4)  |  |

| <u>7.33</u> | Config5 register (CP0 Register 16, Select 5)  |  |

| <u>7.34</u> | GSConfig register (CP0 Register 16, Select 6) |  |

| <u>7.35</u> | LLAddr register (CP0 Register 17, Select 0)   |  |

| <u>7.36</u> | XContext register (CP0 Register 20, Select 0) |  |

|          | <u>7.37</u> | Diag register (CP0 Register 22, Select 0)                    |              |            |

|----------|-------------|--------------------------------------------------------------|--------------|------------|

|          | <u>7.38</u> | GSCause register (CP0 Register 22, Select 1)                 |              |            |

|          | <u>7.39</u> | VPID register (CP0 Register 22, Select 2)                    |              |            |

|          | <u>7.40</u> | Debug register (CP0 Register 23, Select 0)                   |              |            |

|          | <u>7.41</u> | DEPC register (CP0 Register 24, Select 0)                    |              |            |

|          | <u>7.42</u> | PerfCnt register (CP0 Register 25, Select 0 ~ 7)             |              |            |

|          | <u>7.43</u> | ErrCtl register (CP0 Register 26, Select 0)                  |              |            |

|          | <u>7.44</u> | CacheErr register (CP0 Register 27, Select 0)                |              |            |

|          | <u>7.45</u> | CacheErr1 register (CP0 Register 27, Select 1)               |              |            |

|          | <u>7.46</u> | TagLo register (CP0 Register28, Select 0)                    |              |            |

|          | <u>7.47</u> | DataLo Register (CP0 Register 28, Select 1)                  |              |            |

|          | <u>7.48</u> | TagHi register (CP0 Register 29, Select 0)                   |              |            |

|          | <u>7.49</u> | DataHi Register (CP0 Register 29, Select 1)                  |              |            |

|          | <u>7.50</u> | ErrorEPC register (CP0 Register 30, Select 0)                |              |            |

|          | <u>7.51</u> | DESAVE register (CP0 Register 31, Select 0)                  |              |            |

|          | <u>7.52</u> | KScratch1 ~ 6 registers (CP0 Register 31, Select 2 ~ 7)      |              |            |

| <u>8</u> | Processor   | r performance analysis and optimization                      |              | <u>.</u>   |

|          | <u>8.1</u>  | Performance counter organization form and access method      |              | <u>14</u>  |

|          | <u>8.1</u>  | 1 Processor Core Performance Counter                         | 144          |            |

|          | <u>8.1</u>  | 2 Shared cache performance counter                           | 144          |            |

|          | <u>8.2</u>  | Processor performance count events                           | <u>. 145</u> |            |

|          | <u>8.2</u>  | 1 Definition of processor core performance count events      | 1            | <u>145</u> |

|          | <u>8.2</u>  | <u>2</u> Definition of shared cache performance count events |              | <u>54</u>  |

|          |             |                                                              |              |            |

IV

Page 9

## Godson 3A2000 / 3B2000 Processor User Manual • Next

# Figure catalog

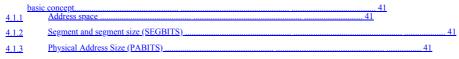

| Figure 2-1 FPU floating point data format                                                   |           | <u> 9</u> |          |

|---------------------------------------------------------------------------------------------|-----------|-----------|----------|

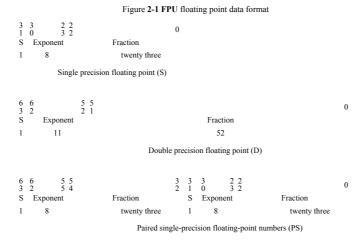

| Figure 2-2 FPU fixed-point data format                                                      |           |           |          |

| Figure 2-3 FIR register format                                                              |           |           |          |

| Figure 2-4 FCSR register format                                                             |           |           |          |

| Figure 2-5 FCCR register format                                                             | <u>13</u> |           |          |

| Figure 2-6 FEXR register format                                                             | 14        |           |          |

| Figure 2-7 FENR register format                                                             | 14        |           |          |

| Figure 2-8 Address Resolution Format of Index Class CACHE Instruction                       |           |           | <u>.</u> |

| Figure 4-1 xkphys segment virtual address resolution                                        |           | 43        |          |

| Figure 5-1 Loongson 3A2000 chip processor storage hierarchy                                 |           | <u>53</u> |          |

| Figure 5-2 Schematic diagram of the primary instruction cache line                          |           |           |          |

| Figure 5-3 Schematic diagram of the primary data cache line structure                       |           |           | 55       |

| Figure 5-4 Schematic diagram of the secondary sacrifice cache line structure                |           | 56        |          |

| Figure 5-5 Schematic diagram of three-level shared cache line                               |           |           |          |

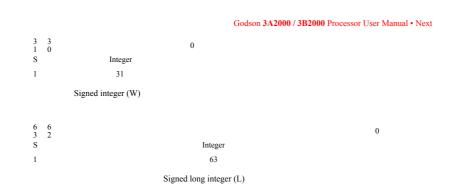

| Figure 5-6 Cache state transition under the consistency protocol                            |           | 59        |          |

| Figure 7-1 Index register format                                                            |           |           |          |

| Figure 7-2 Random register format                                                           |           |           |          |

| Figure 7-3 EntryLo0 and EntryLo1 register format when accessed by DMFC0 / DMTC0 instruction |           |           |          |

| Figure 7-4 EntryLo0 and EntryLo1 register format when accessed by MFC0 / MTC0 instruction   |           |           |          |

| Figure 7-5 Context register format                                                          |           |           |          |

| Figure 7-6 UserLocal register format                                                        |           |           |          |

| Figure 7-7 PageMask Register Format                                                         |           |           |          |

| Figure 7-8 PageGrain register format                                                        |           |           |          |

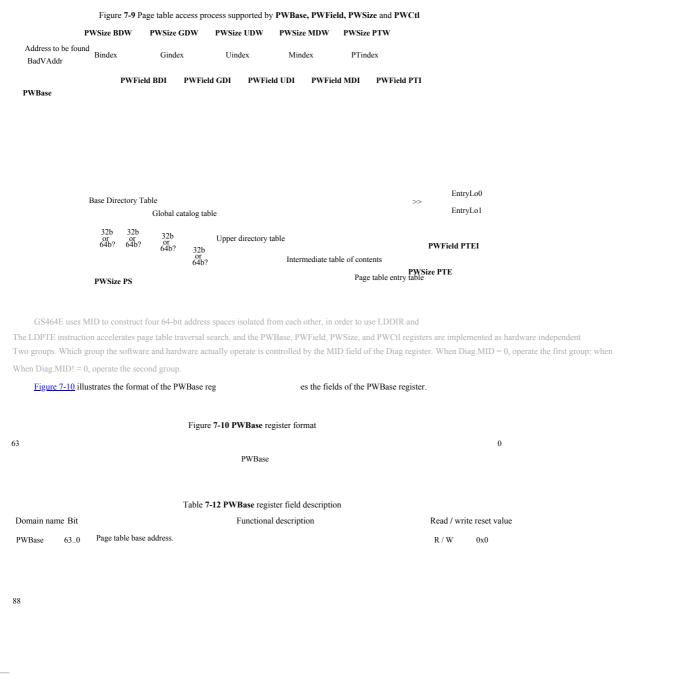

| Figure 7-9 Page table access process supported by PWBase, PWField, PWSize and PWCtl |            | 88 |

|-------------------------------------------------------------------------------------|------------|----|

| Figure 7-10 PWBase register format                                                  |            |    |

| Figure 7-11 PWField register format                                                 |            |    |

| Figure 7-12 PWSize register format                                                  | <u></u>    |    |

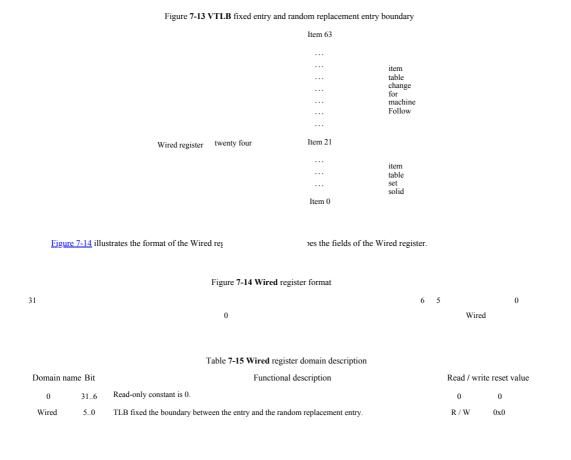

| Figure 7-13 Boundary of fixed entry and random replacement entry in VTLB            |            |    |

| Figure 7-14 Wired register format                                                   | <u> 91</u> |    |

| Figure 7-15 PWCtl register format                                                   | <u></u>    |    |

| Figure 7-16 HWREna register format                                                  |            |    |

| Figure 7-17 BadVAddr Register Format                                                | <u></u>    |    |

| Figure 7-18 Count register format                                                   | <u></u>    |    |

| Figure 7-19 GSEBase register format                                                 | <u></u>    |    |

| Figure 7-20 PGD register format                                                     | <u></u>    |    |

| Figure 7-21 EntryHi Register Format                                                 |            |    |

| Figure 7-22 Compare register format                                                 |            |    |

| Figure 7-23 Status register format                                                  | 101        |    |

| Figure 7-24 IntCtl register format                                                  |            |    |

| Figure 7-25 SRSCtl register format                                                  |            |    |

| Figure 7-26 Cause register format                                                   | 105        |    |

Page 10

V

| Godson <b>3A2000</b> / <b>3B2000</b> Pro                                                            | cessor User Manual • | Next  |

|-----------------------------------------------------------------------------------------------------|----------------------|-------|

| Figure 7-27 EPC register format                                                                     |                      |       |

| Figure 7-28 PRId register format                                                                    |                      |       |

| Figure 7-29 EBase register format                                                                   |                      |       |

| Figure 7-30 Config register format                                                                  | 110                  |       |

| Figure 7-31 Config1 register format                                                                 |                      |       |

| Figure 7-32 Config2 register format                                                                 |                      |       |

| Figure 7-33 Config3 register format                                                                 |                      |       |

| Figure 7-34 Config4 register format                                                                 |                      |       |

| Figure 7-35 Config5 register format                                                                 |                      |       |

| Figure 7-36 GSConfig register format                                                                |                      |       |

| Figure 7-37 LLAddr register format                                                                  |                      |       |

| Figure 7-38 XContext register format                                                                |                      |       |

| Figure 7-39 Diag Register Format                                                                    |                      |       |

| Figure 7-40 GSCause register format                                                                 |                      |       |

| Figure 7-41 VPID register format                                                                    |                      |       |

| Figure 7-42 DEPC register format                                                                    |                      |       |

| Figure 7-43 PerfCnt Control Register Format                                                         |                      |       |

| Figure 7-44 PerfCnt Counter Register Format                                                         |                      |       |

| Figure 7-45 ErrCtl register format                                                                  |                      |       |

| Figure 7-46 The format of the CacheErr register used for I-Cache check error information            |                      |       |

| Figure 7-47 The format of the CacheErr register when D-Cache is used to check the error information |                      |       |

| Figure 7-48 CacheErr1 register format                                                               |                      |       |

| Figure 7-49 The format of the TagLo register used to access the I-Cache Tag                         |                      | 135   |

| Figure 7-50 The format when the TagLo register is used to access the D-Cache Tag                    |                      | 135   |

| Figure 7-51 The format of the TagLo register used to access the V-Cache Tag                         |                      |       |

| Figure 7-52 The format of the TagLo register used to access the S-Cache Tag                         |                      |       |

| Figure 7-53 The format of the TagLo register used to access Cache Data at all levels                |                      | 137   |

| Figure 7-54 The format of the DataLo register used for I-Cache access                               |                      |       |

| Figure 7-55 The format of the TagHi register used to access various levels of Cache Tag             |                      |       |

| Figure 7-56 The format of TagHi register used to access Cache Data at all levels                    |                      | . 139 |

| Figure 7-57 The format of the DataHi register used for I-Cache access                               |                      | 140   |

| Figure 7-58 ErrorEPC register format                                                                |                      |       |

| Figure 7-59 DESAVE register format                                                                  |                      |       |

| Figure 7-60 KScratch <i>n</i> register format                                                       |                      |       |

VI

# Page 11

## Godson 3A2000 / 3B2000 Processor User Manual • Next

# Table directory

| Table 2-1 CPU instruction set: memory access instruction                          | 3       |

|-----------------------------------------------------------------------------------|---------|

| Table 2-2 Operation instructions: arithmetic instructions (ALU immediate data)    | 4       |

| Table 2-3 Operation instructions: arithmetic instructions (3 operands)            |         |

| Table 2-4 Operation instructions: arithmetic instructions (2 operands)            |         |

| Table 2-5 Operation instructions: multiplication and division instructions        |         |

| Table 2-6 Operation instructions: shift instructions                              |         |

| Table 2-7 Jump and branch instructions                                            |         |

| Table 2-8 Coprocessor 0 instructions                                              |         |

| Table 2-9 Other instructions: special instructions                                |         |

| Table 2-10 Other instructions: Exception caught instruction                       |         |

| Table 2-11 Other commands: conditional move commands                              |         |

| Table 2-12 Other instructions: No operation                                       |         |

| Table 2-13 Relevant parameters of floating point format                           |         |

| Table 2-14 The calculation method of floating point value V                       |         |

| Table 2-15 Maximum and minimum values of floating point numbers                   |         |

| Table 2-16 FIR Register Field Description                                         |         |

| Table 2-17 FCSR Register Field Description                                        |         |

| Table 2-18 Rounding Mode (RM) Encoding                                            |         |

| Table 2-19 Default handling of floating-point exceptions                          |         |

| Table 2-20 Floating-point branch jump instruction                                 |         |

| Table 2-21 Floating-point operation instructions                                  |         |

| Table 2-22 Floating-point branch jump instructions                                |         |

| Table 2-23 Floating-point branch jump instructions                                |         |

| Table 2-24 Floating-point branch jump instructions                                |         |

| Table 2-25 Floating-point branch jump instructions                                |         |

| Table 2-26 Correspondence between CACHE instruction op [1: 0] and cache hierarchy |         |

| Table 2-27 Loongson extended memory access instructions                           |         |

| Table 2-28 Godson extended arithmetic and logic operation instructions            |         |

| Table 2-29 Godson Extended X86 Binary Translation Acceleration Instructions       |         |

| Table 2-30 Godson Extended ARM Binary Translation Acceleration Instructions       |         |

| Table 2-31 Loongson extended 64-bit multimedia acceleration instructions          |         |

| Table 2-32 Godson Extended Miscellaneous Instructions                             |         |

| Table 3-1 Judgment basis of processor mode                                        |         |

| Table 4-1 Host Address Space Division and Access Control                          |         |

| Table 4-2 TLB management related CP0 registers                                    |         |

| Table 4-3 TLB Management Related Privileged Instructions                          |         |

| Table 5-1 Cache parameters                                                        | <u></u> |

| Table 5-2 Three-level shared cache bank selection bits and index address          |         |

| Table 5-3 CACHE command in root mode                                              |         |

| Table 6-1 Exception Priority                                                      |         |

| Table 6-2 Exception vector base address                                           |         |

| Table 5-4 Interrupt reguest generation in compatible interrupt mode       75         Table 5-6 Interrupt reguest generation in compatible interrupt mode       75         Table 5-1 Interrupt reguest reference       72         Table 5-1 Interrupt mode information       72         Table 7-1 Root Connecessor 0 Register List       77         Table 7-2 Index register field description       80         Table 7-4 EntryLoD and EntryLoI register field description when Accessed by MFCO/ MTCO instruction       82         Table 7-5 EntryLoD and EntryLoI register field description when accessed by MFCO/ MTCO instruction       82         Table 7-4 EntryLoD and EntryLoI register field Description       84         Table 7-4 Daye Mask Register Field Description       85         Table 7-10 Daye Register Field Description       84         Table 7-10 Paye Mask Register Field Description       82         Table 7-11 Paye Crain Register Field Description       82         Table 7-12 PWBase register field Description       82         Table 7-13 PWField Register Field Description       90         Table 7-14 PWC Register Field Description       92         Table 7-15 PWFAR Register Field Description       92         Table 7-16 PWC Register Field Description       92         Table 7-17 PWFAR Register Field Description       92         Table 7-16 PWC Register                               | Table 6-3 Exception Vector Offset                                                                     | <u> 66</u>  |             |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------|-------------|

| Table 6-6 Internut mode Judgment       75         Table 7-1 Root Corprocessor O Register List       72         Table 7-2 Index register field description       80         Table 7-2 Index register field description when accessed by MFC0 / MTC0 instruction is accessed       81         Table 7-5 IntryLo0 and EntryLo1 register field description when accessed by MFC0 / MTC0 instruction       82         Table 7-5 Cache attribute coding table       83         Table 7-5 Discription of Context register domain       84         Table 7-10 Dask field encoding and page size       86         Table 7-10 PaseMask Register Field Description       86         Table 7-10 PaseMask Register Field Description       86         Table 7-10 PaseMask Register Field Description       87         Table 7-10 PaseMask Register Field Description       88         Table 7-10 PaseMask Register Field Description       88         Table 7-110 PaseTable Register Field Description       89         Table 7-10 PaseMask Register Field Description       90         Table 7-10 PaseMask Register Field Description       92         Table 7-10 PaseMask Register Field Description       <                                    | Table 6-4 Interrupt request generation in compatible interrupt mode                                   |             |             |

| Table 7-1 Root Coprocess of Register List       77         Table 7-2 Index register field description       79         Table 7-2 Index register field description when DMFCO / DMTCO instruction is accessed       81         Table 7-2 Index register field description when accessed by MFCO / MTCO instruction       82         Table 7-2 Cache attribute coding table       81         Table 7-2 For the register domain description       82         Table 7-2 PareAdask Register Field Description       86         Table 7-2 PareAdask Register Field Description       86         Table 7-10 Mask field encoding and gate size       86         Table 7-10 Mask field encoding and gate size       86         Table 7-10 Mask field encoding and gate size       86         Table 7-12 PWHate register Field Description       87         Table 7-12 PWHate register Field Description       81         Table 7-12 PWHate register Field Description       82         Table 7-14 PWSize Register Field Description       91         Table 7-15 PWCH Register Field Description       92         Table 7-16                                                                   | Table 6-5 Priority relationship between interrupts in vector interrupt mode                           |             | 75          |

| Table 7-1 Root Coprocess of Register List       77         Table 7-2 Index register field description       79         Table 7-2 Index register field description when DMFCO / DMTCO instruction is accessed       81         Table 7-2 Index register field description when accessed by MFCO / MTCO instruction       82         Table 7-2 Cache attribute coding table       81         Table 7-2 For the register domain description       82         Table 7-2 PareAdask Register Field Description       86         Table 7-2 PareAdask Register Field Description       86         Table 7-10 Mask field encoding and gate size       86         Table 7-10 Mask field encoding and gate size       86         Table 7-10 Mask field encoding and gate size       86         Table 7-12 PWHate register Field Description       87         Table 7-12 PWHate register Field Description       81         Table 7-12 PWHate register Field Description       82         Table 7-14 PWSize Register Field Description       91         Table 7-15 PWCH Register Field Description       92         Table 7-16                                                                   | Table 6-6 Interrupt mode judgment                                                                     |             |             |

| Table 7-3 Random register field description       \$0         Table 7-4 Emryl, of and Enryl, of register field description when DMECO/DMTCO instruction is accessed.       \$1         Table 7-4 Cache attribute coding table       \$2         Table 7-4 Cache attribute coding table       \$1         Table 7-4 Cache attribute coding table       \$2         Table 7-4 Cache attribute coding table       \$2         Table 7-4 Cache attribute coding and page size       \$6         Table 7-4 Cache attribute coding and page size       \$8         Table 7-10 PageMask Register Field Description       \$8         Table 7-10 PageMask Register Field Description       \$8         Table 7-11 PageCrain Register Field Description       \$8         Table 7-12 PWBase register Field Description       \$8         Table 7-13 PWField Register Field Description       \$9         Table 7-14 PWBize Register Field Description       \$9         Table 7-15 Wird register field description       \$9         Table 7-16 PWCH Register Field Description       \$9         Table 7-16 PWCH Register Field Description       \$9         Table 7-16 PWCH Register Field Description       \$9         Table 7-17 HWR Fina register field description       \$9         Table 7-16 PWCH Register Field Description       \$9         Table 7-20 Exercintion of Compare Regi                                              |                                                                                                       |             |             |

| Table 7-4 EntryLo0 and EntryLo1 register field description when DMFC0 / DMTC0 instruction is accessed       \$1         Table 7-5 Cache attribute coding table       \$3         Table 7-4 Cache attribute coding table       \$3         Table 7-5 Description of Context register domain       \$4         Table 7-5 Description of Context register domain       \$6         Table 7-5 User coal register Gonain description       \$6         Table 7-10 Mask field encoding and tage size       \$6         Table 7-10 Wask register Field Description       \$7         Table 7-11 PageGrain Register Field Description       \$8         Table 7-12 WMase register field description       \$8         Table 7-12 WMase register field Description       \$9         Table 7-12 WMase register field Description       \$9         Table 7-14 PWCin Register Field Description       \$9         Table 7-14 PWCin Register Field Description       \$2         Table 7-15 Vinct Register Field Description       \$2         Table 7-16 Description of Compare Register Field       \$6         Table 7-21 PCD Register                                               | Table 7-2 Index register field description                                                            | <u></u>     |             |

| Table 7-5 Entyl-00 and Entyl-01 register field description when accessed by MFC0 / MTC0 instruction       \$2         Table 7-6 Cache attribute coding table       \$3         Table 7-7 Description of Context register domain description       \$8         Table 7-9 UserLocal register Field Description       \$8         Table 7-10 PageMask Register Field Description       \$8         Table 7-11 PageCrain Register Field Description       \$8         Table 7-12 PWBase register Field Description       \$8         Table 7-14 PWField Register Field Description       \$8         Table 7-14 PWField Register Field Description       \$8         Table 7-15 Wired register Field Description       \$9         Table 7-16 PWCitt Register Field Description       \$9         Table 7-10 Count register field description       \$9         Table 7-20 Description of GSEBas register Field       \$9         Table 7-20 Description of Compare Register Field       \$100         Table 7-20 Encyfilti register Field Description       \$9         Table 7-20 Encyfilti register Field Description       \$100      <                                  | Table 7-3 Random register field description                                                           |             |             |

| Table 7-6 Cache attribute coding table       83         Table 7-7 Description of Context register domain       84         Table 7-8 Usert coal register field Description       85         Table 7-10 Mask field encoding and page size       86         Table 7-10 Mask field encoding and page size       86         Table 7-10 Mask field encoding and page size       86         Table 7-11 PageGrain Register Field Description       87         Table 7-12 PWBase register Field Description       89         Table 7-14 PWR Register Field Description       90         Table 7-14 PWR Register Field Description       91         Table 7-16 PWCH Register Field Description       91         Table 7-16 PWCH Register Field Description       92         Table 7-16 PWCH Register Field Description       91         Table 7-16 PWCH Register Field Description       92         Table 7-17 HWR Fin register field description       91         Table 7-16 DWCH Register Field Description       92         Table 7-20 Description of GSEBase register field       96         Table 7-21 PGD Register Field Description       92         Table 7-22 EntryHi register Field Description       92         Table 7-23 EntryHi register Field Description       100         Table 7-24 StattsRegister Field Description       101                                                                                               | Table 7-4 EntryLo0 and EntryLo1 register field description when DMFC0 / DMTC0 instruction is accessed |             |             |

| Table 7-7 Description of Context register domain       84         Table 7-8 UserLocal register domain description       85         Table 7-9 DageMask Register Field Description       86         Table 7-10 Mask field encoding and page size       86         Table 7-11 Dayscfmin Register Field Description       87         Table 7-12 PWBase register field description       88         Table 7-13 PWField Register Field Description       89         Table 7-14 PWSize Register Field Description       90         Table 7-15 Wired register Field Description       91         Table 7-16 PWGite Register Field Description       92         Table 7-17 HWREna register field description       91         Table 7-18 Description of BadVAddr register field       94         Table 7-19 Count register field description       92         Table 7-19 Count register Field Description       92         Table 7-20 Description of GSEBase register field       94         Table 7-21 RD Register Field Description       92         Table 7-22 Entrylli register field Description       92         Table 7-23 Description of Compare Register Field       100         Table 7-24 Status Register Field Description       101         Table 7-25 Entrylli register Field Description       103         Table 7-26 StacCl Register Field Description                                                                        | Table 7-5 EntryLo0 and EntryLo1 register field description when accessed by MFC0 / MTC0 instruction   |             |             |

| Table 7-8 UserLocal register domain description       85         Table 7-9 PageMask Register Field Description       86         Table 7-10 Mask field encoding and page size       86         Table 7-11 PageGrain Register Field Description       87         Table 7-13 PWField Register Field Description       89         Table 7-14 PWSize Register Field Description       90         Table 7-15 Wired Register Field Description       91         Table 7-16 PWCIR Register Field Description       92         Table 7-10 Count register field description       93         Table 7-20 Description of GSEBase register Field       96         Table 7-21 PCIR Register Field Description       92         Table 7-22 Description of Compare Register Field       100         Table 7-23 Description of Compare Register Field       101         Table 7-24 Status Register Field Description       103         Table 7-25 InCI Register Field Description       105 </td <td>Table 7-6 Cache attribute coding table</td> <td> 83</td> <td></td> | Table 7-6 Cache attribute coding table                                                                | 83          |             |

| Table 7-9 PageMask Register Field Description       86         Table 7-10 Mask field encoding and page size       86         Table 7-11 PageGrain Register Field Description       87         Table 7-12 PWBase register Field Description       88         Table 7-12 PWBase register Field Description       90         Table 7-13 PWField Register Field Description       90         Table 7-15 Wired register Field Description       91         Table 7-16 PWC11 Register Field Description       92         Table 7-17 HWREna register field description       92         Table 7-18 Description of BadVAddr register field       94         Table 7-19 Count register field description       93         Table 7-19 Count register field description       95         Table 7-20 Description of GSEBase register field       96         Table 7-21 PGD Register Field Description       97         Table 7-22 EnryHi register field description       98         Table 7-23 Description of Compare Register Field       100         Table 7-24 Status Register Field Description       103         Table 7-25 EnryHi register field Description       103         Table 7-26 SRSCU Register Field Description       105         Table 7-26 SRSCU Register Field Description       105         Table 7-26 SRSCU Register Field Description       10                                                                           | Table 7-7 Description of Context register domain                                                      |             |             |

| Table 7-10 Mask field encoding and page size       86         Table 7-11 PageGrain Register Field Description       87         Table 7-12 PWBase register Field Description       88         Table 7-12 PWField Register Field Description       89         Table 7-14 PWSize Register Field Description       90         Table 7-14 PWSize Register Field Description       91         Table 7-16 PWCI Register Field Description       92         Table 7-17 HWREna register field description       93         Table 7-18 Description of Bad VAddr register field       94         Table 7-18 Description of GSBase register field       94         Table 7-20 Description of GSBase register field       96         Table 7-21 PGD Register Field Description       92         Table 7-22 Description of GSBase register Field       96         Table 7-23 Description of GSBase register Field       96         Table 7-24 Status Register Field Description       97         Table 7-25 IntCit Register Field Description       100         Table 7-25 ExcOate codes and their corresponding exception types       105         Table 7-20 FEC Register Field Description       105         Table 7-23 ExcOate codes codes and their corresponding exception types       105         Table 7-24 Status Register Field Description       106         Table 7-23                                                                  | Table 7-8 UserLocal register domain description                                                       |             |             |

| Table 7-11 PageGrain Register Field Description       \$7         Table 7-12 PWBase register Field Description       \$8         Table 7-13 PWField Register Field Description       \$9         Table 7-14 PWSize Register Field Description       90         Table 7-15 Wired register Field Description       91         Table 7-16 PWCill Register Field Description       92         Table 7-17 HWREna register Field Description       92         Table 7-18 Description of BadVAddr register field       94         Table 7-19 Count register field description       93         Table 7-20 Description of GSEBase register field       96         Table 7-20 Register Field Description       97         Table 7-21 PGD Register Field Description       97         Table 7-22 EntryHir register field description       98         Table 7-23 LintyHir register Field Description       100         Table 7-24 Status Register Field Description       101         Table 7-25 SRSCH Register Field Description       103         Table 7-28 ExcOde codes and their corresponding exception types       105         Table 7-30 FRI Register Field Description       105         Table 7-30 FRI Register Field Description       105         Table 7-29 ENC Register Field Description       105         Table 7-30 FRI Register Field Description       <                                                                    | Table 7-9 PageMask Register Field Description                                                         |             |             |

| Table 7-12 PWBase register field description       88         Table 7-13 PWField Register Field Description       90         Table 7-14 PWSize Register Field Description       91         Table 7-15 Wred register Field Description       91         Table 7-16 PWCil Register Field Description       92         Table 7-16 PWCil Register Field Description       92         Table 7-17 HWREna register field description       93         Table 7-18 Description of BadVAddr register field       94         Table 7-20 Count register field description       95         Table 7-20 Description of GSEBase register field       96         Table 7-21 PGD Register Field Description       97         Table 7-22 EntryHi register field description       97         Table 7-23 Description of Compare Register Field       100         Table 7-24 Status Register Field Description       101         Table 7-25 IntCil Register Field Description       103         Table 7-26 SRSCil Register Field Description       104         Table 7-20 Exerciption of Cause register field       105         Table 7-20 Exerciption of Cause register field Description       105         Table 7-20 Exerciption of Cause register field Description       105         Table 7-20 Exerciption of Cause register field Description       105         Table 7-30 PRId                                                                   | Table 7-10 Mask field encoding and page size                                                          |             |             |

| Table 7-13 PWField Register Field Description89Table 7-14 PWSize Register Field Description90Table 7-15 Wired register Field Description91Table 7-16 PWCtl Register Field Description92Table 7-17 HWREna register field description93Table 7-18 Description of BadVAddr register field94Table 7-18 Description of BadVAddr register field94Table 7-19 Count register field description95Table 7-20 Description of GSEBase register field96Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register Field Description98Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCil Register Field Description103Table 7-28 EstxCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description106Table 7-29 EPC Register Field Description107Table 7-31 Ebase Register Field Description110Table 7-32 Config Register Field Description110Table 7-34 Config Register Field Description111Table 7-34 Config Register Field Description112Table 7-34 Config Register Field Description112Table 7-34 Config Register Field Description112Table 7-34 Config Register Field Description113Table 7-34 Config Register Field Description113Table 7-34 Config Register Field Description114Table 7-34 C                                                                                | Table 7-11 PageGrain Register Field Description                                                       |             |             |

| Table 7-14 PWSize Register Field Description90Table 7-15 Wired register Field Description91Table 7-16 PWCtl Register Field Description92Table 7-17 HWREna register field description93Table 7-18 Description of BadVAddr register field94Table 7-19 Count register field description95Table 7-20 Description of GSEBase register field96Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register field description97Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCtl Register Field Description103Table 7-26 SRSCtl Register Field Description104Table 7-27 Description of Cause register field105Table 7-28 ExcCode codes and their corresponding exception types105Table 7-30 PRId Register Field Description108Table 7-31 EBase Register Field Description109Table 7-32 Config Register Field Description110Table 7-33 Config Register Field Description112Table 7-34 Config Legister Field Description112Table 7-35 Config Register Field Description113Table 7-36 Config Register Field Description113Table 7-37 Config Register Field Description113Table 7-36 Config Register Field Description113Table 7-37 Config Register Field Description113Table 7-36 Config Register Field Description115Table 7-37                                                                                 | Table 7-12 PWBase register field description                                                          |             |             |

| Table 7-15 Wired register field description91Table 7-16 PWCtl Register Field Description92Table 7-17 HWREna register field description93Table 7-18 Description of BadVAddr register field94Table 7-19 Count register field description95Table 7-19 Count register field description95Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register field description98Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 EntryHi register Field Description103Table 7-26 SRSCtl Register Field Description103Table 7-27 Description of Cause register field105Table 7-28 ExcCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description107Table 7-30 PRId Register Field Description108Table 7-31 EBase Register Field Description109Table 7-32 Config Register Field Description110Table 7-33 Config Register Field Description112Table 7-34 Config Register Field Description113Table 7-35 Config Register Field Description113Table 7-37 Config Register Field Description115Table 7-37 Config Register Field Description112Table 7-37 Config                                                                                | Table 7-13 PWField Register Field Description                                                         |             |             |

| Table 7-16 PWCU Register Field Description92Table 7-17 HWREna register field description93Table 7-18 Description of BadVAddr register field94Table 7-19 Count register field description95Table 7-19 Count register field description95Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register field description98Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCl Register Field Description103Table 7-26 SRSCH Register Field Description104Table 7-27 Description of Cause register field105Table 7-28 ExcCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description108Table 7-30 PRI Register Field Description108Table 7-31 EBase Register Field Description110Table 7-32 Config Register Field Description112Table 7-33 Config Register Field Description112Table 7-34 Config Register Field Description113Table 7-35 Config Register Field Description113Table 7-37 Config Register Field Description113Table 7-37 Config Register Field Description115Table 7-37 Config Register Field Description115Table 7-37 Config Register Field Description112Table 7-37 Config Register Field Description113Table 7-37 Config Register Field Description114                                                                                                    | Table 7-14 PWSize Register Field Description                                                          |             |             |

| Table 7-17 HWREna register field description93Table 7-18 Description of BadVAddr register field94Table 7-19 Count register field description95Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register field description98Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCil Register Field Description103Table 7-26 SRSCtl Register Field Description104Table 7-27 Description of Cause register field105Table 7-28 ExeCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description107Table 7-31 EBase Register Field Description109Table 7-32 Config Register Field Description111Table 7-35 Config Register Field Description112Table 7-36 Config Register Field Description113Table 7-37 Config Register Field Description113Table 7-36 Config Register Field Description115Table 7-37 Config Register Field Description113Table 7-36 Config Register Field Description115Table 7-37 Config Register Field Description115Table 7-38 GSConfig Register Field Description117Table 7-37 Config Register Field Description112Table 7-38 GSConfig Register Field Description112Table 7-37 Config Register Field Description115Table 7-38 GSConfig Register Field Description116 <td>Table 7-15 Wired register field description</td> <td><u></u></td> <td></td>    | Table 7-15 Wired register field description                                                           | <u></u>     |             |

| Table 7-18 Description of BadVAddr register field94Table 7-19 Count register field description95Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register field description98Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCil Register Field Description103Table 7-26 SRSCtl Register Field Description104Table 7-27 Description of Cause register field105Table 7-28 ExeCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description107Table 7-30 ERGister Field Description108Table 7-31 EBase Register Field Description109Table 7-32 Config Register Field Description110Table 7-33 Config 1 register Field Description112Table 7-34 Config Register Field Description113Table 7-35 Config Register Field Description113Table 7-36 Config Register Field Description115Table 7-37 Config Register Field Description115Table 7-36 GSConfig Register Field Description117Table 7-37 Config Register Field Description117Table 7-37 Config Register Field Description118                                                                                                                                                                                                                                                                                        | Table 7-16 PWCtl Register Field Description                                                           |             |             |

| Table 7-19 Count register field description95Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register field description98Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCl Register Field Description103Table 7-26 SRSCII Register Field Description103Table 7-27 Description of Cause register field105Table 7-28 ExcCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description107Table 7-30 PRId Register Field Description108Table 7-32 Config Register Field Description110Table 7-32 Config Register Field Description112Table 7-34 Config Register Field Description113Table 7-35 Config Register Field Description113Table 7-36 Config Register Field Description115Table 7-37 Config Register Field Description117Table 7-38 Config Register Field Description117Table 7-35 Config Register Field Description117                                                                                                                                                                                                                                                                                                                                                                                                                                        | Table 7-17 HWREna register field description                                                          |             |             |

| Table 7-20 Description of GSEBase register field96Table 7-21 PGD Register Field Description97Table 7-22 EntryHi register field description98Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCtl Register Field Description103Table 7-26 SRSCtl Register Field Description104Table 7-27 Description of Cause register field105Table 7-28 ExcCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description107Table 7-30 PRId Register Field Description108Table 7-32 Config Register Field Description110Table 7-32 Config Register Field Description111Table 7-34 Config Register Field Description112Table 7-35 Config Register Field Description113Table 7-36 Config Register Field Description115Table 7-37 Config Register Field Description117Table 7-37 Config Register Field Description118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Table 7-18 Description of BadVAddr register field                                                     |             |             |

| Table 7-21 PGD Register Field Description       97         Table 7-22 EntryHi register field description       98         Table 7-23 Description of Compare Register Field       100         Table 7-24 Status Register Field Description       101         Table 7-25 IntCH Register Field Description       103         Table 7-26 SRSCH Register Field Description       104         Table 7-27 Description of Cause register field       105         Table 7-28 ExcCode codes and their corresponding exception types       105         Table 7-29 EPC Register Field Description       107         Table 7-31 EBase Register Field Description       108         Table 7-32 Config Register Field Description       110         Table 7-32 Config Register Field Description       110         Table 7-32 Config Register Field Description       111         Table 7-32 Config Register Field Description       112         Table 7-32 Config Register Field Description       112         Table 7-32 Config Register Field Description       112         Table 7-32 Config Register Field Description       113         Table 7-32 Config Register Field Description       113         Table 7-36 Config Register Field Description       115         Table 7-37 Config Register Field Description       115         Table 7-37 Config Register Field Descri                                                                  | Table 7-19 Count register field description                                                           |             |             |

| Table 7-22 EntryHi register field description       98         Table 7-23 Description of Compare Register Field       100         Table 7-24 Status Register Field Description       101         Table 7-25 IntCtl Register Field Description       103         Table 7-26 SRSCtl Register Field Description       104         Table 7-26 SRSCtl Register Field Description       104         Table 7-26 SRSCtl Register Field Description       104         Table 7-27 Description of Cause register field       105         Table 7-28 ExeCode codes and their corresponding exception types       105         Table 7-29 EPC Register Field Description       107         Table 7-30 PRId Register Field Description       108         Table 7-31 EBase Register Field Description       109         Table 7-32 Config Register Field Description       110         Table 7-34 Config 2 Register Field Description       111         Table 7-34 Config 2 Register Field Description       112         Table 7-35 Config 3 Register Field Description       113         Table 7-36 Config 4 Register Field Description       115         Table 7-37 Config 5 Register Field Description       115         Table 7-37 Config 5 Register Field Description       117         Table 7-38 GSConfig Register Field Description       117                                                                                                | Table 7-20 Description of GSEBase register field                                                      | <u></u>     |             |

| Table 7-23 Description of Compare Register Field100Table 7-24 Status Register Field Description101Table 7-25 IntCtl Register Field Description103Table 7-26 SRSCtl Register Field Description104Table 7-27 Description of Cause register field105Table 7-28 ExcCode codes and their corresponding exception types105Table 7-29 EPC Register Field Description107Table 7-20 EPC Register Field Description108Table 7-30 PRId Register Field Description109Table 7-31 EBase Register Field Description110Table 7-32 Config Register Field Description111Table 7-34 Config2 Register Field Description112Table 7-36 Config4 register Field Description113Table 7-37 Config5 Register Field Description117Table 7-38 GSConfig Register Field Description117Table 7-38 GSConfig Register Field Description118                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Table 7-21 PGD Register Field Description                                                             |             |             |