Multi-core processor architecture, register description and system software programming guide

V1.5

Loongson Zhongke Technology Co., Ltd.

The copyright of this document belongs to Loongson Zhongke Technology Co., Ltd. and reserves all rights. Without written permission, any company and individual No one may publicize, reprint or otherwise distribute any part of this document to third parties. Otherwise, the law will be investigated Legal responsibility.

### Disclaimer

This document only provides periodic information, and the content can be updated at any time according to the actual situation of the product without notice. Ruin The company does not assume any responsibility for direct or indirect losses caused by improper use of documents.

## Loongson Zhongke Technology Co., Ltd.

Loongson Technology Corporation Limited Address: Building 2, Longxin Industrial Park, Zhongguancun Environmental Protection Technology Demonstration Park, Haidian District, Beijing Building No. 2, Loongson Industrial Park, Zhongguancun Environmental Protection Park, Haidian District, Beijing Telephone (Tel): 010-62546668 Fax: 010-62600826

Page 3

Reading guide

"Loongson 3A4000 Processor Register User Manual" introduces Loongson 3A4000 multi-core processor architecture and register description.

The chip system architecture, function and configuration of main modules, register list and bit fields are described in detail.

| revise history                                    |            |      |                                                                                          |                                                                |  |

|---------------------------------------------------|------------|------|------------------------------------------------------------------------------------------|----------------------------------------------------------------|--|

| Document update record                            |            | 1    | Document name:                                                                           | Loongson 3A4000 processor register user manual                 |  |

|                                                   |            |      | version number                                                                           | V1.5                                                           |  |

|                                                   |            |      | founder                                                                                  | Chip R & D Department                                          |  |

|                                                   |            | С    | reation date                                                                             | 2019-12-20                                                     |  |

| Update history                                    |            |      |                                                                                          |                                                                |  |

| Serial numbe#pdated version number update content |            |      | update content                                                                           |                                                                |  |

| 1                                                 | 2018-05-08 | V0.1 | initial version                                                                          |                                                                |  |

| 2                                                 | 2018-05-28 | V0.2 | Update various chip configuration registers                                              |                                                                |  |

| 3                                                 | 2018-06-02 | V0.3 | Add frequency division control chapter, update GPIO, UART, I2C, SPI content              |                                                                |  |

| 4                                                 | 2018-06-04 | V0.4 | Modify route                                                                             |                                                                |  |

| 5                                                 | 2018-06-05 | V0.5 | Modify the memory controller section, add software clock system                          |                                                                |  |

| 6                                                 |            |      | Add clock description; add GPIO interrupt description; add temperature status detection; |                                                                |  |

|                                                   | 2018-06-13 | V0.6 | Add HT interrupt description; add 3A3000 compatible description; modify EXTIoi,          |                                                                |  |

|                                                   |            |      | Support 8-node int                                                                       | erconnection; modify the processor core description.           |  |

| 7                                                 | 2018-09-11 | V0.7 | Update the configu                                                                       | ration register list and add some register field descriptions. |  |

| 8                                                 | 2018-09-13 | V0.8 | Updated stable clock structure description.                                              |                                                                |  |

| 9  | 2018-10-26 | V0.9 | Update DDR section                                                                                                                             |

|----|------------|------|------------------------------------------------------------------------------------------------------------------------------------------------|

| 10 | 2019-02-19 | V1.0 | Internal debug version                                                                                                                         |

| 11 | 2019-05-29 | V1.1 | Update configuration register, temperature sensor, stable counter, expansion<br>Interrupt, Scache interrupt, processor CPUCFG part description |

| 12 | 2019-07-01 | V1.2 | Modified some statement errors                                                                                                                 |

| 13 | 2019-09-11 | V1.3 | Chapter 4 adds some feature control instructions<br>11.1.1 Fix int_edge address offset                                                         |

| 14 | 2019-10-11 | V1.4 | 12.5 Correction of temperature sensor register description                                                                                     |

| 15 | 2019-12-17 | V1.5 | Fix some format errors                                                                                                                         |

Manual feedback: service@loongson.cn

You can also submit chip production to our company through the problem feedback website http://bugs.loongnix.org/

Godson 3A4000 processor register user manual directory

Problems in the use of products, and obtain technical support.

## Page 6

## table of Contents

| 1 Overview                                                       | 1            |

|------------------------------------------------------------------|--------------|

| 1.1 Introduction to Loongson series processors                   | 1            |

| 1.2 Introduction to Godson 3A4000                                | 2            |

| 2 System Configuration and Control                               | <u>5</u>     |

| 2.1 Chip working mode                                            | <u>5</u>     |

| 2.2 Description of control pins                                  | <u>5</u>     |

| 3 Physical address space distribution                            |              |

| 3.1 Physical address space distribution between nodes            |              |

| 3.2 Physical address space distribution within the node          |              |

| 3.3 Address Routing Distribution and Configuration               |              |

| 4 Chip Configuration Register                                    |              |

| 4.1 Version register (0x0000)                                    |              |

| 4.2 Chip characteristic register (0x0008)                        |              |

| <u>4.3 Vendor name (0x0010)</u>                                  | <u>17</u>    |

| <u>4.4 Chip name (0x0020)</u>                                    |              |

| 4.5 Function setting register (0x0180)                           |              |

| 4.6 Pin drive setting register (0x0188)                          |              |

| 4.7 Function sampling register (0x0190)                          |              |

| 4.8 Temperature sampling register (0x0198)                       |              |

| 4.9 Bias Configuration Register (0x01A0)                         | 20           |

| 4.10 Frequency configuration register (0x01B0)                   | 20           |

| 4.11 Processor core frequency division setting register (0x01D0) | twenty two   |

| 4.12 Processor core reset control register (0x01D8)              | twenty three |

| 4.13 Routing setting register (0x0400)                           | twenty three |

| 4.14 Other function setting register (0x0420)                    | twenty four  |

| 4.15 Celsius temperature register (0x0428)                       |              |

| 4.16 SRAM adjustment register (0x0430)                           |              |

| 4.17 FUSE0 observation register (0x0460)                         |              |

| 4.18 FUSE1 observation register (0x0470)                         |              |

Ι

| 5.1 Introduction to Chip Module Clock                       |               |

|-------------------------------------------------------------|---------------|

| 5.2 Frequency division and enable control of processor core | <br>          |

| 5.2.1 Access by address                                     |               |

| 5.2.2 Configuration register instruction access             |               |

| 5.3 Node clock frequency division and enable control        | <br>. 29      |

| 5.3.1 Software settings                                     |               |

| 5.3.2 Automatic hardware settings                           |               |

| 5.4 HT controller frequency division and enable control     | <br><u>81</u> |

| 5.5 Stable Counter Frequency Division and Enable Control    | <br>32        |

| Software clock system                                       |               |

| 6.1 Stable Counter                                          |               |

| 6.1.1 Stable Timer configuration address                    |               |

| 6.1.2 Clock Control of Stable Counter                       |               |

| 6.1.3 Stable Counter Calibration                            |               |

| 6.2 Node Counter                                            |               |

| 6.2.1 Access by address                                     |               |

| 6.2.2 Configuration register instruction access             |               |

| 6.3 Summary of Clock System                                 |               |

| GPIO control                                                |               |

| 7.1 Output enable register (0x0500)                         |               |

| 7.2 Input Output Register (0x0508)                          |               |

| 7.3 Interrupt Control Register (0x0510)                     |               |

| 7.4 GPIO pin function multiplexing table                    |               |

| 7.5 GPIO interrupt control                                  |               |

| GS464V processor core                                       |               |

| 8.1 Instruction set features implemented by 3A4000          | <br>. 42      |

| 8.2 3A4000 Configuration Status Register Access             |               |

| Shared Cache (SCache)                                       |               |

| Interrupt and communication between processor cores         | <br>50        |

Π

| 10.2 Configuration register instruction access       |            |

|------------------------------------------------------|------------|

| 11 I / O interruption                                | 54         |

| 11.1 Traditional I / O Interrupt                     |            |

| 11.1.1 Access by address                             | <u> 56</u> |

| 11.1.2 Configuration register instruction access     |            |

| 11.2 Expansion I / O Interrupt                       |            |

| 11.2.1 Access by address                             | <u> 58</u> |

| 11.2.2 Instruction access to configuration registers | <u> 61</u> |

| 11.2.3 Extended IO interrupt trigger register        | <u>61</u>  |

| <br> |  | 61 |  |

|------|--|----|--|

| 11.2.4 Differences between extended IO interrupt handling and tradition | nal HT interru | upt handling |    |

|-------------------------------------------------------------------------|----------------|--------------|----|

| 12 Temperature sensor                                                   |                | <u> 63</u>   |    |

| 12.1 Real-time temperature sampling                                     |                |              |    |

| 12.2 High and low temperature interrupt trigger                         |                |              |    |

| 12.3 High temperature automatic frequency reduction setting             |                |              | 65 |

| 12.4 Temperature state detection and control                            |                | <u> 66</u>   |    |

| 12.5 Control of temperature sensor                                      | 67             | <u>'</u>     |    |

| 13 DDR3 / 4 SDRAM controller configuration                              |                |              |    |

| 13.1 DDR3 / 4 SDRAM Controller Function Overview                        |                |              |    |

| 13.2 DDR3 / 4 SDRAM Read Operation Protocol                             |                |              |    |

| 13.3 DDR3 / 4 SDRAM Write Operation Protocol                            |                | <u></u>      |    |

| 13.4 DDR3 / 4 SDRAM parameter configuration format                      |                | <u>71</u>    |    |

| 13.4.1 Parameter list of memory controller                              |                |              |    |

| 13.5 Software Programming Guide                                         |                |              |    |

| 13.5.1 Initialization                                                   | <u> 83</u>     |              |    |

| 13.5.2 Control of reset pin                                             |                |              |    |

| 13.5.3 Leveling                                                         | <u>35</u>      |              |    |

| 13.5.4 Power control configuration process                              |                |              |    |

| 13.5.5 Initiate MRS commands separately                                 |                | 87           |    |

| 13.5.6 Arbitrary operation control bus                                  |                | 88           |    |

| 13.5.7 Self-loop test mode control                                      |                |              |    |

| 13.5.8 ECC function usage control                                       |                | 2            |    |

|                                                                         |                |              |    |

III

| 13.5.9 Observation of Error Status                                |            | 89         |            |            |

|-------------------------------------------------------------------|------------|------------|------------|------------|

| 14 HyperTransport Controller                                      | <u> 93</u> |            |            |            |

| 14.1 HyperTransport hardware setup and initialization             |            |            | <u> 93</u> |            |

| 14.2 HyperTransport Protocol Support                              |            | <u>96</u>  |            |            |

| 14.3 HyperTransport interrupt support                             |            |            |            |            |

| 14.3.1 PIC Interrupt                                              |            | 97         |            |            |

| 14.3.2 Local Interrupt Handling                                   |            | 97         |            |            |

| 14.3.3 Extended interrupt handling                                |            |            | <u> 98</u> |            |

| 14.4 HyperTransport Address Window                                |            |            |            |            |

| 14.4.1 HyperTransport Space                                       | <u>98</u>  |            |            |            |

| 14.4.2 Internal window configuration of HyperTransport controller |            |            |            | <u> 99</u> |

| 14.5 Configuration Register                                       |            |            | 100        |            |

| 14.5.1 Bridge Control                                             | 104        |            |            |            |

| 14.5.2 Capability Registers                                       | 104        |            |            |            |

| 14.5.3 Error Retry Control Register                               | 107        |            |            |            |

| 14.5.4 Retry Count Register                                       | 10         | 7          |            |            |

| 14.5.5 Revision ID Register                                       | 108        |            |            |            |

| 14.5.6 Interrupt Discovery & Configuration                        |            |            |            |            |

| 14.5.7 Interrupt Vector Register                                  |            | <u>109</u> |            |            |

| 14.5.8 Interrupt Enable Register                           |

|------------------------------------------------------------|

| 14.5.9 Link Train Register                                 |

| 14.5.10 Receive Address Window Configuration Register      |

| 14.5.11 Configuration Space Conversion Register            |

| 14.5.12 POST address window configuration register         |

| 14.5.13 Prefetchable Address Window Configuration Register |

| 14.5.14 UNCACHE Address Window Configuration Register      |

| 14.5.15 P2P Address Window Configuration Register          |

| 14.5.16 Controller Parameter Configuration Register        |

| 14.5.17 Receive Diagnostic Register                        |

| 14.5.18 PHY Status Register                                |

| 14.5.19 Command send buffer size register                  |

IV

| 14.5.20 Data transmission buffer size register               |     |

|--------------------------------------------------------------|-----|

| 14.5.21 Send Buffer Debug Register                           |     |

| 14.5.22 Receive buffer initial register                      | 133 |

| 14.5.23 Training 0 Timeout Short Timer Register              |     |

| 14.5.24 Training 0 Time-out timer register                   | 134 |

| 14.5.25 Training 1 Count Register                            | 134 |

| 14.5.26 Training 2 Count Register                            | 135 |

| 14.5.27 Training 3 Count Register                            | 135 |

| 14.5.28 Software Frequency Configuration Register            |     |

| 14.5.29 PHY Impedance Matching Control Register              |     |

| 14.5.30 PHY Configuration Register                           |     |

| 14.5.31 Link Initialization Debug Register                   |     |

| 14.5.32 LDT debug register                                   |     |

| 14.5.33 HT TX POST ID window configuration register          |     |

| 14.5.34 External Interrupt Conversion Configuration          |     |

| 14.6 Access method of HyperTransport bus configuration space |     |

| 14.7 HyperTransport Multiprocessor Support                   |     |

| 15 Low-speed IO controller configuration                     |     |

| 15.1 UART Controller                                         |     |

| 15.1.1 Data Register (DAT)                                   | 147 |

| 15.1.2 Interrupt Enable Register (IER)                       |     |

| 15.1.3 Interrupt Identification Register (IIR)               |     |

| 15.1.4 FIFO Control Register (FCR)                           |     |

| 15.1.5 Line Control Register (LCR)                           |     |

| 15.1.6 MODEM Control Register (MCR)                          |     |

| 15.1.7 Line Status Register (LSR)                            |     |

| 15.1.8 MODEM Status Register (MSR)                           | 154 |

| 15.1.9 Receive FIFO count value (RFC)                        | 154 |

|                                                              |     |

V

| 15.1.10 Transmit FIFO count value (TFC)<br>15.1.11 Frequency Division Latch |          |

|-----------------------------------------------------------------------------|----------|

| 15.1.12 Use of newly added registers                                        | <u>í</u> |

Page 11

| 15.2 SPI Controller                                        |     |

|------------------------------------------------------------|-----|

| 15.2.1 Control Register (SPCR)                             |     |

| 15.2.2 Status Register (SPSR)                              | 158 |

| 15.2.3 Data Register (TxFIFO)                              |     |

| 15.2.4 External Register (SPER)                            |     |

| 15.2.5 Parameter control register (SFC_PARAM)              |     |

| 15.2.6 Chip Select Control Register (SFC_SOFTCS)           |     |

| 15.2.7 Timing Control Register (SFC_TIMING)                |     |

| 15.2.8 Custom Control Register (CTRL)                      |     |

| 15.2.9 Custom Command Register (CMD)                       |     |

| 15.2.10 Custom Data Register 0 (BUF0)                      | 161 |

| 15.2.11 Custom Data Register 1 (BUF1)                      | 162 |

| 15.2.12 Custom timing register 0 (TIMER0)                  |     |

| 15.2.13 Custom Timing Register 1 (TIMER1)                  |     |

| 15.2.14 Custom Timing Register 2 (TIMER2)                  |     |

| 15.2.15 SPI two-wire four-wire user guide                  |     |

| 15.3 I2C Controller                                        |     |

| 15.3.1 Lower Latch Register (PRERIo)                       |     |

| 15.3.2 Frequency divider latch high byte register (PRERhi) |     |

| 15.3.3 Control Register (CTR)                              |     |

| 15.3.4 Transmit Data Register (TXR)                        |     |

| 15.3.5 Receive Data Register (RXR)                         |     |

| 15.3.6 Command Control Register (CR)                       |     |

| 15.3.7 Status Register (SR)                                |     |

| 15.3.8 Slave Device Control Register (SLV_CTRL)            |     |

| 16 3A3000 kernel compatibility                             |     |

| 16.1 Compatible with 3A3000 kernel                         |     |

| 16.1.1 Method for identifying processor characteristics    |     |

| 16.1.2 Current kernel modification method                  |     |

| 16.2 New feature support                                   |     |

| 16.2.1 Identification of processor characteristics         |     |

VI

|   | 16.2.2 Extended interrupt mode                            |  |

|---|-----------------------------------------------------------|--|

| 1 | 16.3 Configuration register instruction debugging support |  |

Page 13

Godson 3A4000 processor register user manual diagram directory

# Figure catalog

| Figure 1-1 Loongson No. 3 system structure                             | 1          |    |

|------------------------------------------------------------------------|------------|----|

| Figure 1-2 Godson No. 3 node structure                                 | 2          |    |

| Figure 1-3 Godson 3A4000 chip structure                                |            |    |

| Figure 6-1 Stable reset control when multiple chips are interconnected |            | 35 |

| Figure 8-1 GS464V structure diagram                                    | 42         |    |

| Figure 11-1 Loongson 3A4000 processor interrupt routing diagram        | 54         |    |

| Figure 13-1 DDR3 SDRAM read operation protocol                         | <u> 70</u> |    |

| Figure 13-2 DDR3 SDRAM write operation protocol                      | <u> 71</u> |

|----------------------------------------------------------------------|------------|

| Figure 14-1 HT protocol configuration access in Loongson 3A4000      |            |

| Figure 14-2 Four-piece Loongson No. 3 interconnect structure         |            |

| Figure 14-3 Eight piece Loongson No. 3 interconnection structure     |            |

| Figure 14-4 Two-chip Loongson No. 3 8-bit interconnection structure  |            |

| Figure 14-5 Two-chip Loongson No. 3 16-bit interconnection structure | 146        |

VIII

## Page 14

## Godson 3A4000 processor register user manual table list

# Table directory

| Table 2-1 Control pin description   5                                   |          |    |             |

|-------------------------------------------------------------------------|----------|----|-------------|

| Table 3-1 Node-level system global address distribution                 |          | 7_ |             |

| Table 3-2 Address distribution within the node                          |          |    |             |

| Table 3-3 SCID_SEL address bit settings                                 |          |    |             |

| Table 3-4 Distribution of 44-bit physical addresses in nodes            |          | 8  |             |

| Table 3-5 The space access attributes corresponding to the MMAP field   | <u></u>  | 9  |             |

| Table 3-6 Address Window Register Table                                 | 9        |    |             |

| Table 3-7 Correspondence between the slave device number and the module |          |    | <u>. 15</u> |

| Table 3-8 The space access attributes corresponding to the MMAP field   | <u></u>  | 15 |             |

| Table 4-1 Version Register   17                                         |          |    |             |

| Table 4-2 Chip feature register   17                                    |          |    |             |

| Table 4-3 Vendor Name Register         18                               |          |    |             |

| Table 4-4 Chip Name Register         18                                 |          |    |             |

| Table 4-5 Function Setting Register         18                          | <u>8</u> |    |             |

| Table 4-6 Pin drive setting register         19                         |          |    |             |

| Table 4-7 Function sampling register   1                                | <u>9</u> |    |             |

| Table 4-8 Temperature sampling register                                    |              |              |

|----------------------------------------------------------------------------|--------------|--------------|

| Table 4-9 Bias Setting Register                                            |              |              |

| Table 4-10 Node clock software frequency multiplication setting register   |              | twenty one   |

| Table 4-11 Memory clock software frequency multiplication setting register |              | twenty one   |

| Table 4-12 Processor core software frequency division setting register     |              | twenty two   |

| Table 4-13 Processor core software frequency division setting register     |              | twenty three |

| Table 4-14 Chip Routing Setting Register                                   | twenty three |              |

| Table 4-15 Other function setting registers                                | twenty four  |              |

| Table 4-16 Temperature observation register                                |              |              |

| Table 4-17 Processor core SRAM adjustment registers                        |              |              |

| Table 4-18 FUSE Observation Register                                       |              |              |

| Table 4-19 FUSE Observation Register                                       |              |              |

| Table 5-1 Processor core software frequency division setting register      |              | 28           |

|                                                                            |              |              |

IX

Page 15

| Table 5-2 Other function setting registers                                                     |            |            |            |

|------------------------------------------------------------------------------------------------|------------|------------|------------|

| Table 5-3 Other function setting registers         29                                          |            |            |            |

| Table 5-4 Processor core private divider register         29                                   |            |            |            |

| Table 5-5 Function Setting Register         30                                                 |            |            |            |

| Table 5-6 Other function setting registers         30                                          |            |            |            |

| Table 5-7 Description of high-temperature down-frequency control register                      |            | 30         |            |

| Table 5-8 Function Setting Register                                                            |            |            |            |

| Table 5-9 Other function setting registers   32                                                |            |            |            |

| Table 5-10 Other function setting registers                                                    |            |            |            |

| Table 5-11 GPIO Output Enable Register         32                                              |            |            |            |

| Table 6-1 Address access method         33                                                     |            |            |            |

| Table 6-2 Configuration register instruction access method                                     | <u> 34</u> |            |            |

| Table 6-3 Register meaning   34                                                                |            |            |            |

| Table 6-4 Other function setting registers     34                                              |            |            |            |

| Table 6-5 Node counter register   36                                                           |            |            |            |

| Table 7-1 Output enable register                                                               |            |            |            |

| Table 7-2 Input and Output Registers   37                                                      |            |            |            |

| Table 7-3 Interrupt Control Register   37                                                      |            |            |            |

| Table 7-4 GPIO function reuse table         38                                                 |            |            |            |

| Table 7-5 Interrupt Control Register   39                                                      |            |            |            |

| Table 8-1 List of configuration information of instruction set functions implemented by 3A4000 |            |            | <u> 43</u> |

| Table 8-2 List of Configuration Status Registers in the Core                                   | 46         |            |            |

| Table 9-1 Shared Cache Lock Window Register Configuration                                      | <u> 48</u> |            |            |

| Table 10-1 Inter-processor interrupt related registers and their functional descriptions       |            |            |            |

| Table 10-2 List of Internuclear Interrupts and Communication Registers of Processor Core 0     |            | <u> 50</u> |            |

| Table 10-3 List of Internuclear Interrupts and Communication Registers of Processor Core 1     | <u></u>    | 51         |            |

| Table 10-4 List of Internuclear Interrupts and Communication Registers of Processor Core 2     | <u></u>    | <u> 51</u> |            |

| Table 10-5 List of Internuclear Interrupts and Communication Registers of Processor Core 3 | . 51 |

|--------------------------------------------------------------------------------------------|------|

| Table 10-6 List of interrupts and communication registers between current processor cores  | 52   |

| Table 10-7 Communication Register between Processor Cores                                  |      |

| Table 11-1 Interrupt Control Register                                                      |      |

Х

## Page 16

| Table 11-2 IO Control Register Address                                     | 5 <u>6</u> |

|----------------------------------------------------------------------------|------------|

| Table 11-3 Interrupt Routing Register Description                          |            |

| Table 11-4 Interrupt Routing Register Address                              | <u>56</u>  |

| Table 11-5 Processor core private interrupt status register                |            |

| Table 11-6 Other function setting registers                                | <u> 57</u> |

| Table 11-7 Extended IO interrupt enable register                           |            |

| Table 11-8 Extended IO interrupt auto-rotation enable register             |            |

| Table 11-9 Extended IO Interrupt Status Register                           |            |

| Table 11-10 Extended IO interrupt status register for each processor core  |            |

| Table 11-11 Interrupt pin routing register description                     | <u></u>    |

| Table 11-12 Interrupt Routing Register Address                             | <u> 59</u> |

| Table 11-13 Interrupt target processor core routing register description   | <u>60</u>  |

| Table 11-14 Interrupt Target Processor Core Routing Register Address       |            |

| Table 11-15 Interrupt target node mapping mode configuration               |            |

| Table 11-16 Current processor core's extended IO interrupt status register |            |

| Table 11-17 Extended IO interrupt trigger register                         | <u>61</u>  |

| Table 12-1 Description of Temperature Sampling Register                    |            |

| Table 12-2 Extended IO interrupt trigger register                          |            |

| Table 12-3 High and low temperature interrupt register description         |            |

| Table 12-4 Description of High Temperature Down Frequency Control Register |            |

| Table 12-5 Temperature state detection and control register description    |            |

| Table 12-6 Description of Temperature Sensor Configuration Register        |            |

| Table 12-7 Description of Temperature Sensor Data Register                 |            |

| Table 12-8 Description of temperature sensor monitoring points             |            |

| Table 13-1 DDR3 / 4 Address Control Signal Multiplexing                    |            |

| Table 13-2 List of visible parameters of the memory controller software    |            |

| Table 13-3 No. 0 Memory Controller Error Status Observation Register       |            |

| Table 13-4 No. 1 Memory Controller Error Status Observation Register       |            |

| Table 14-1 HyperTransport bus related pin signals                          | <u> 94</u> |

| Table 14-2 Commands that the HyperTransport receiver can receive           | <u></u>    |

| Table 14-3 Commands to be sent out in two modes                            | <u> 96</u> |

#### Godson 3A4000 processor register user manual table list

| Table 14-4 Other function setting registers                                           | 98                    |            |

|---------------------------------------------------------------------------------------|-----------------------|------------|

| Table 14-5 The default address window distribution of the four HyperTransport interfa | <u>ces</u>            | <u> 98</u> |

| Table 14-6 Address window distribution inside HyperTransport interface of Loongson    | No. 3 processor       | <u> 99</u> |

| Table 14-7 Address window provided in HyperTransport interface of Loongson 3A400      | <u>0 processor 99</u> |            |

| Table 14-8 Definition of Bus Reset Control Register                                   |                       |            |

| Table 14-9 Definition of Command, Capabilities Pointer, Capability ID Register        |                       |            |

| Table 14-10 Link Config, Link Control register definition                             | 105                   |            |

| Table 14-11 Definition of Revision ID, Link Freq, Link Error, Link Freq Cap Registers | <u></u>               |            |

| Table 14-12 Definition of Feature Capability Register                                 |                       |            |

| Table 14-13 Error Retry Control Register     107                                      |                       |            |

| Table 14-14 Retry Count Register                                                      |                       |            |

| Table 14-15 Revision ID Register                                                      |                       |            |

| Table 14-16 Interrupt Capability Register Definition                                  | 108                   |            |

| Table 14-17 Dataport register definition                                              | <u>. 109</u>          |            |

| Table 14-18 IntrInfo register definition (1)                                          | <u>109</u>            |            |

| Table 14-19 IntrInfo register definition (2)                                          | <u>109</u>            |            |

| Table 14-20 HT Bus Interrupt Vector Register Definition (1)                           | <u>111</u>            |            |

| Table 14-21 HT Bus Interrupt Vector Register Definition (2)                           | <u>111</u>            |            |

| Table 14-22 Definition of HT bus interrupt vector register (3)                        |                       |            |

| Table 14-23 HT Bus Interrupt Vector Register Definition (4)                           | <u>111</u>            |            |

| Table 14-24 Definition of HT Bus Interrupt Vector Register (6)                        |                       |            |

| Table 14-25 Definition of HT Bus Interrupt Vector Register (7)                        |                       |            |

| Table 14-26 Definition of HT Bus Interrupt Vector Register (8)                        | 112                   |            |

| Table 14-27 Definition of HT Bus Interrupt Enable Register (1)                        |                       |            |

| Table 14-28 Definition of HT Bus Interrupt Enable Register (2)                        |                       |            |

| Table 14-29 Definition of HT Bus Interrupt Enable Register (3)                        |                       |            |

| Table 14-30 Definition of HT Bus Interrupt Enable Register (4)                        |                       |            |

| Table 14-31 Definition of HT Bus Interrupt Enable Register (5)                        |                       |            |

| Table 14-32 Definition of HT Bus Interrupt Enable Register (6)                        |                       |            |

| Table 14-33 Definition of HT Bus Interrupt Enable Register (7)                        | 115                   |            |

| Table 14-34 Definition of HT Bus Interrupt Enable Register (8)                        |                       |            |

|                                                                                       |                       |            |

XII

Page 18

| Table 14-35 Link Train Register 115                                                                |

|----------------------------------------------------------------------------------------------------|

| Table 14-36 HT Bus Receive Address Window 0 Enable (External Access) Register Definition           |

| Table 14-37 HT Bus Receive Address Window 0 Base Address (External Access) Register Definition 117 |

| Table 14-38 HT Bus Receive Address Window 1 Enable (External Access) Register Definition           |

| Table 14-39 HT Bus Receive Address Window 1 Base Address (External Access) Register Definition     |

| Table 14-40 HT Bus Receive Address Window 2 Enable (External Access) Register Definition           |

| Table 14-41 HT Bus Receive Address Window 2 Base Address (External Access) Register Definition     |

| F                                                                                              |

|------------------------------------------------------------------------------------------------|

| Table 14-42 HT Bus Receive Address Window 3 Enable (External Access) Register Definition 118   |

| Table 14-43 HT Bus Receive Address Window 3 Base Address (External Access) Register Definition |

| Table 14-44 HT Bus Receive Address Window 4 Enable (External Access) Register Definition       |

| Table 14-45 HT Bus Receive Address Window 4 Base Address (External Access) Register Definition |

| Table 14-46 Definition of Extended Address Translation Register in Configuration Space         |

| Table 14-47 Definition of Extended Address Translation Register                                |

| Table 14-48 HT Bus POST Address Window 0 Enable (Internal Access) 121                          |

| Table 14-49 HT Bus POST Address Window 0 Base Address (Internal Access) 121                    |

| Table 14-50 HT Bus POST Address Window 1 Enable (Internal Access) 121                          |

| Table 14-51 HT Bus POST Address Window 1 Base Address (Internal Access)                        |

| Table 14-52 HT Bus Prefetchable Address Window 0 Enable (Internal Access) 122                  |

| Table 14-53 HT Bus Prefetchable Address Window 0 Base Address (Internal Access) 122            |

| Table 14-54 HT Bus Prefetchable Address Window 1 Enable (Internal Access) 123                  |

| Table 14-55 HT Bus Prefetchable Address Window 1 Base Address (Internal Access)                |

| Table 14-56 HT Bus Uncache Address Window 0 Enable (Internal Access)                           |

| Table 14-57 HT Bus Uncache Address Window 0 Base Address (Internal Access)                     |

| Table 14-58 HT Bus Uncache Address Window 1 Enable (Internal Access)                           |

| Table 14-59 HT Bus Uncache Address Window 1 Base Address (Internal Access) 125                 |

| Table 14-60 HT Bus Uncache Address Window 2 Enable (Internal Access)                           |

| Table 14-61 HT Bus Uncache Address Window 2 Base Address (Internal Access)                     |

| Table 14-62 HT Bus Uncache Address Window 3 Enable (Internal Access)                           |

| Table 14-63 HT Bus Uncache Address Window 3 Base Address (Internal Access)                     |

| Table 14-64 Definition of HT Bus P2P Address Window 0 Enable (External Access) Register 126    |

| Table 14-65 HT Bus P2P Address Window 0 Base Address (External Access) Register Definition 127 |

| ХШ                                                                                             |

|                                                                                                |

# Page 19

| Table 14-66 Definition of HT Bus P2P Address Window 1 Enable (External Access) Regis | ster 127     |

|--------------------------------------------------------------------------------------|--------------|

| Table 14-67 HT Bus P2P Address Window 1 Base Address (External Access) Register Det  | finition 127 |

| Table 14-68 Definition of Controller Parameter Configuration Register 0              |              |

| Table 14-69 Definition of Controller Parameter Configuration Register 1              |              |

| Table 14-70 Receive Diagnostic Register                                              | <u>130</u>   |

| Table 14-71 PHY Status Register                                                      |              |

| Table 14-72 Command Send Buffer Size Register                                        |              |

| Table 14-73 Data transmission buffer size register                                   | 131          |

| Table 14-74 Send Buffer Debug Register                                               | 2            |

| Table 14-75 Initial Register of Receive Buffer                                       | 133          |

| Table 14-76 Training 0 Timeout Short Timer Register                                  | 134          |

| Table 14-77 Training 0 Timeout Long Count Register                                   | 134          |

| Table 14-78 Training 1 Count Register   134                                          |              |

| Table 14-79 Training 2 Count Register   135                                          |              |

| Table 14-80 Training 3 Count Register   135                                          |              |

| Table 14-81 Software Frequency Configuration Register                                |              |

| Table 14-82 Impedance Matching Control Register           Table 14-83 PHY Configuration Register |           |

|--------------------------------------------------------------------------------------------------|-----------|

| Table 14-84 Link Initialization Debug Register                                                   |           |

| Table 14-85 LDT debug register 1                                                                 |           |

| Table 14-86 LDT debug register 2                                                                 |           |

| Table 14-87 LDT debug register 3                                                                 |           |

| Table 14-88 LDT debug register 4 140                                                             |           |

| Table 14-89 LDT debug register 5                                                                 |           |

| Table 14-90 LDT Debug Register 5                                                                 |           |

| Table 14-91 HT TX POST ID WIN0                                                                   |           |

| Table 14-92 HT TX POST ID WIN1                                                                   |           |

| Table 14-93 HT TX POST ID WIN2                                                                   |           |

| Table 14-94 HT TX POST ID WIN3                                                                   | <u>1</u>  |

| Table 14-95 HT RX INT TRANS LO                                                                   | 12        |

| Table 14-96 HT RX INT TRANS Hi                                                                   | <u>42</u> |

XIV

## Page 20

| Table 15-1 SPI Controller Address Space Distribution       |            |

|------------------------------------------------------------|------------|

| Table 16-1 Chip Feature Register                           |            |

| Table 16-2 Manufacturer Name Register                      |            |

| Table 16-3 Chip Name Register                              | <u>169</u> |

| Table 16-4 HT RX INT TRANS LO                              |            |

| Table 16-5 HT RX INT TRANS Hi                              |            |

| Table 16-6 Other function setting registers                |            |

| Table 16-7 Communication Registers between Processor Cores |            |

XV

#### Loongson 3A4000 processor register user manual

### 1 Overview

#### 1.1 Introduction to Loongson series processors

Loongson processor mainly includes three series. Loongson No. 1 processor and its IP series are mainly for embedded applications.

Core 2 superscalar processor and its IP series are mainly for desktop applications, and Godson 3 multi-core processor series is mainly for service

Server and high-performance machine applications. According to the needs of the application, some of Loongson 2 can also face some high-end embedded

Yes, some low-end Loongson 3 can also be used for some desktop applications. The above three series are developed in parallel.

Loongson No. 3 multi-core series processor is based on a scalable multi-core interconnect architecture design, integrating multiple high-end on a single chip Performance processor core and a large number of level 2 caches, and also realize the interconnection of multiple chips through high-speed I / O interface to form a larger Modular system.

The scalable interconnection structure adopted by Loongson 3 is shown in Figure 1-1 below. Loongson No. 3 on-chip and multi-chip systems pass similar Of the interconnection ports are implemented in units of nodes, where each node consists of 8 \* 8 crossbar switches, each The switch connects four processor cores and four shared caches, and connects the four directions of east (E) south (N) west (W) north (N) The other nodes are interconnected.

|                  | P0 P1 P2 P3        |                  |     |

|------------------|--------------------|------------------|-----|

| E<br>S<br>W<br>N | 8x8 switch         | E<br>S<br>W<br>N |     |

|                  | L2 L2 L2 L2<br>(A) | (B)              | (C) |

Loongson No. 3 node and two-dimensional interconnection structure, (a) node structure, (b) 2 \* 2 mesh network connected to 16 processors, (c) The 4 \* 4 mesh network connects 64 processors.

#### Figure 1-1 Loongson No. 3 system structure

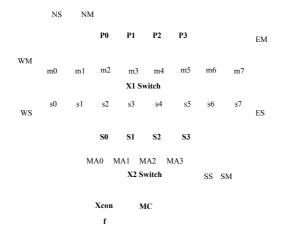

The structure of Loongson No. 3 node is shown in Figure 1-2 below. Each node has two levels of AXI crossbars connected to the processor and shared

Cache, memory controller and IO controller. Among them, the first level AXI crossbar switch (called X1 Switch, referred to as X1)

Connect the processor and shared cache. The second level crossbar switch (called X2 Switch, referred to as X2 for short) is connected to share Cache and Memory controller.

Figure 1-2 Loongson No. 3 node structure

In each node, up to 8 \* 8 X1 crossbars are connected to four GS464 processor cores through four Master ports

(P0, P1, P2, P3 in the figure), connected to four interleave shared caches with four slave ports through four slave ports

Block (S0, S1, S2, S3 in the figure), connected to the four directions of east, south, west and north through four pairs of Master / Slave

Other nodes or IO nodes (EM / ES, SM / SS, WM / WS, NM / NS in the figure).

The X2 crossbar is connected to four shared caches through four Master ports, and one is connected to at least one Slave port Memory controller, at least one Slave port is connected to a crossbar configuration module (Xconf), which is used for Configure the X1 and X2 address windows of this node. You can also connect more memory controllers and IO ports as needed Wait.

## 1.2 Introduction to Godson 3A4000

Loongson 3A4000 is a quad-core Loongson processor, which is manufactured using 28nm process and has a stable operating frequency of 1.5-2.0GHz, the main technical features are as follows:

Four 64-bit super-scalar GS464V high-performance processor cores are integrated on-chip;

2

## Page 23

- On-chip integrated 8MB split shared three-level cache (composed of 4 individual modules, each module has a capacity of 2MB);

- Maintain the cache consistency of multi-core and I / O DMA access through the directory protocol;

- Two 64-bit DDR3 / 4 controllers with ECC and 800MHz are integrated on-chip;

- Two 16-bit HyperTransport controllers (hereinafter referred to as HT) are integrated on-chip;

- Each 16-bit HT port is split into two 8-way HT ports for use;

- Integrate 2 I2C, 1 UART, 1 SPI, 16 GPIO interfaces on-chip.

The top structure design of Loongson 3A4000 is optimized on a large scale based on 3A2000 / 3A3000.

#### Go as follows:

- · Adjusted the on-chip interconnect structure, simplified the address routing, the interconnection between IO modules adopts RING structure;

- Optimized the bandwidth utilization and cross-chip delay of the HT controller;

- Optimized the structure of the memory controller, added support for the memory controller DDR4, and supported the memory slot to connect the accelerator card

- Standardize the configuration register space and access method, and introduce the CSR configuration register access mechanism;

- Optimized the structure of the interrupt controller and supported the vector interrupt hardware distribution mechanism

- Added 8-way interconnection support.

The overall architecture of Loongson 3A4000 chip is based on multi-level interconnection. The structure is shown in Figures 1-3 below.

Figure 1-3 Loongson 3A4000 chip structure

The first level interconnection uses a 5x5 crossbar switch to connect four GS464v cores (as the master device) and four shares

The Cache module (as a slave device) and an IO port are connected to the IO-RING. (IO port uses a Master and

A Slave).

3

Page 24

#### Loongson 3A4000 processor register user manual

The second level interconnection uses a 5x3 crossbar switch to connect 4 shared Cache modules (as the main device), two DDR3 / 4

The memory controller and an IO port are connected to IO-RING.

IO-RING contains 8 ports, the connection includes 4 HT controllers, MISC modules, SE modules and two stages are cross-connected

turn off. The two HT controllers (lo / hi) share the 16-bit HT bus, which is used as two 8-bit HT buses.

lo monopolizes the 16-bit HT bus. A DMA controller is integrated in the HT controller, and the DMA controller is responsible for the DMA control of the IO and

Responsible for maintaining consistency between slices.

The above interconnection structures all use separate data channels for reading and writing. The width of the data channel is 128 bits.

The same frequency of the core is used to provide high-speed on-chip data transmission. In addition, the first-level crossbar connects 4 processor cores with

The read data channel of scache is 256 bits to improve the read bandwidth of the on-chip processor core to access scache.

#### Page 25

4

#### Loongson 3A4000 processor register user manual

## 2 System configuration and control

## 2.1 Chip working mode

According to the structure of the system, Loongson 3A4000 mainly includes two working modes:

- Single chip mode. The system only contains one piece of Godson 3A4000, which is a symmetric multiprocessor system (SMP);

- Multi-chip interconnect mode. The system contains 2, 4, or 8 Loongson 3A4000, which communicate with each other through the HT port

Connected to form a non-uniform memory multiprocessor system (CC-NUMA)

## 2.2 Description of control pins

The main control pins include DO\_TEST, ICCC\_EN, NODE\_ID [2: 0], CLKSEL [9: 0],

#### CHIP\_CONFIG [5: 0].

| Table 2-1 | Control pin | description |

|-----------|-------------|-------------|

|-----------|-------------|-------------|

| signal                                                                                                                                                                                                 | Up and dow       | n                                                                                                               | effect                                                      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------|--|

| DO_TEST                                                                                                                                                                                                |                  | 1'b1 means function                                                                                             | mode                                                        |  |

|                                                                                                                                                                                                        | pull up          | 1'b0 means test mode                                                                                            | e                                                           |  |

|                                                                                                                                                                                                        |                  |                                                                                                                 | ip consistent interconnect mode                             |  |

| ICCC_EN                                                                                                                                                                                                | drop down        | 1'b0 means single ch                                                                                            | ip mode                                                     |  |

| NODE_ID [2: 0]                                                                                                                                                                                         |                  | Indicates the processor number in multi-chip consistent interconnect mode                                       |                                                             |  |

|                                                                                                                                                                                                        | HT clock control |                                                                                                                 | HT clock control                                            |  |

| signal effect<br>1'b1: indicates that the HT PLL clock is controlled by CLKSEL [9: 4]<br>CLKSEL [9] 1'b0: The initial frequency multiplication is 1 frequency multiplication, which can be reconfigure |                  | effect                                                                                                          |                                                             |  |

|                                                                                                                                                                                                        |                  | 1'b1: indicates that the HT PLL clock is controlled by CLKSEL [9: 4]                                            |                                                             |  |

|                                                                                                                                                                                                        |                  | 1'b0: The initial frequency multiplication is 1 frequency multiplication, which can be reconfigured by software |                                                             |  |

|                                                                                                                                                                                                        |                  |                                                                                                                 | Set                                                         |  |

|                                                                                                                                                                                                        |                  |                                                                                                                 | 1'b1: indicates that the HT PLL uses the SYSCLK clock input |  |

CLKSEL [9:0]

CHIP\_CONFIG [5: 0]

6

5

#### Loongson 3A4000 processor register user manual

| CLUCEL 101 |                                                                   |                                                                                |

|------------|-------------------------------------------------------------------|--------------------------------------------------------------------------------|

| CLKSEL [8] | 1'b0: indicates that the HT PLL uses a differential clock input   |                                                                                |

|            |                                                                   | 2'b00 means the PHY clock frequency is 1.6GHz                                  |

|            |                                                                   | 2'b01 indicates that the PHY clock frequency is 3.2GHz (the reference clock is |

|            | CLKSEL [7: 6]                                                     | 1.6GHz at 25MHz)                                                               |

| CLKSEL [5] | 2'b10 means the PHY clock frequency is 1.2GHz                     |                                                                                |

|            | 2'b11 means the PHY clock frequency is 2.4GHz                     |                                                                                |

|            | 1'b1: indicates that the HT PLL clock is in bypass mode, directly |                                                                                |

|            | Use external input 100MHz / 25MHz reference clock                 |                                                                                |

|            |                                                                   |                                                                                |

## Page 26

#### Loongson 3A4000 processor register user manual

CLKSEL [4] 1-Reference clock is 25MHz, 0-Reference clock is 100MHz

MEM clock control (clock frequency should be 1/2 of interface clock)

| CLKSEL [3: 2] | Output frequency                                         |

|---------------|----------------------------------------------------------|

| 2'b00         | 466MHz                                                   |

| 2'b01         | 600MHz                                                   |

| 2'b10         | Software configuration (PLL clock multiplier 1.6-3.2GHz) |

| 2'b11         | SYSCLK (100MHz / 25MHz)                                  |

Main clock control (highest frequency of network and processor core)

| CLKSEL [1:0]               | Output frequency                                                                   |

|----------------------------|------------------------------------------------------------------------------------|

| 2'b00                      | lGHz                                                                               |

| 2'b01                      | 2GHz                                                                               |

| 2'b10                      | Software configuration (PLL clock multiplier 1.6-3.2GHz)                           |

| 2'b11                      | SYSCLK (100MHz / 25MHz)                                                            |

| Chip configuration control |                                                                                    |

| CHIP_CONFIG [0] SE fun     | ction enable                                                                       |

| CHIP_CONFIG [1] Defaul     | t HT Gen1 mode                                                                     |

| CHIP_CONFIG [2] reserve    | 2d                                                                                 |

| CHIP_CONFIG [3] HT0 /      | 1-hi enters the consistency mode by default, which is used to support 8-way mutual |

| ever                       | 1                                                                                  |

| CHIP_CONFIG [4] HT log     | cic function interchange, HT0 / HT1 exchange                                       |

| CHIP_CONFIG [5] On-chi     | p clock debug enable (DCDL)                                                        |

|                            |                                                                                    |

#### Page 27

#### Loongson **3A4000** processor register user manual

#### 3 Physical address space distribution

The system physical address distribution of Loongson No. 3 series processors adopts a globally accessible hierarchical addressing design to

System development is compatible with expansion. The physical address width of the entire system is 48 bits. According to the upper 4 bits of the address, the entire address is empt Time is evenly distributed to 16 nodes, that is, each node is allocated 44-bit address space.

## 3.1 Distribution of physical address space between nodes

Loongson 3A4000 processor can directly use 2/4/8 3A4000 chips to connect directly to build CC-NUMA system, each core

The processor number of the chip is determined by the pin NODEID. The address space of each chip is distributed as follows:

#### Table 3-1 Node-level system global address distribution

| Chip node number (NODEID) | Address [47:44] bits | starting address | End address      |

|---------------------------|----------------------|------------------|------------------|

| 0                         | 0                    | 0x0000_0000_0000 | 0x0FFF_FFFF_FFFF |

| 1                         | 1                    | 0x1000_0000_0000 | 0x1FFF_FFFF_FFFF |

| 2                         | 2                    | 0x2000_0000_0000 | 0x2FFF_FFFF_FFFF |

| 3                         | 3                    | 0x3000_0000_0000 | 0x3FFF_FFFF_FFFF |

| 4                         | 4                    | 0x4000_0000_0000 | 0x4FFF_FFFF_FFFF |

| 5                         | 5                    | 0x5000_0000_0000 | 0x5FFF_FFFF_FFFF |

| 6                         | 6                    | 0x6000_0000_0000 | 0x6FFF_FFFF_FFFF |

| 7                         | 7                    | 0x7000_0000_0000 | 0x7FFF_FFFF_FFFF |

When the number of system nodes is less than 8 nodes, the nodemask field of the routing setting register (0x1fe00400) should be set, When a guess visit occurs, it is guaranteed that even if there is no physical node address, a response can be obtained. (2 channels: 0x1; 4 channels: 0x3)

## 3.2 Physical address space distribution within the node

Godson 3A4000 uses a single-node 4-core configuration, so Godson 3A4000 chip integrated DDR memory controller, HT

The corresponding addresses of the bus are contained in the 44-bit address space from 0x0 (inclusive) to 0x1000\_0000\_0000 (not included).

Within each node, the 44-bit address space is further divided among all devices connected within the node, only if the access type

When it is cached, the request will be routed to 4 shared cache modules. According to the different configuration of chip and system structure, such as

If a slave device is not connected to a port, the corresponding address space is reserved address space and access is not allowed. 7

#### Page 28

Loongson 3A4000 processor register user manual

The slave devices corresponding to the address space of the Loongson 3A4000 chip are as follows:

#### Table 3-2 Address distribution within the node

device Address [43:40] bits Start address in the node Node end address

MC0

4

| MC1               | 5 | 0x500_0000_0000 | 0x5FF_FFFF_FFFF |

|-------------------|---|-----------------|-----------------|

| SE                | c | 0xC00_0000_0000 | 0xCFF_FFFF_FFFF |

| HT0 Lo controller | a | 0xA00_0000_0000 | 0xAFF_FFFF_FFFF |

| HT0 Hi controller | b | 0xB00_0000_0000 | 0xBFF_FFFF_FFFF |

| HT1 Lo controller | e | 0xE00_0000_0000 | 0xEFF_FFFF_FFFF |

| HT1 Hi controller | f | 0xF00_0000_0000 | 0xFFF_FFFF_FFFF |

Unlike the mapping relationship of direction ports, Loongson 3A4000 can decide to share based on the actual application access behavior Cache cross-addressing mode. The address space corresponding to the 4 shared Cache modules in the node is based on two of the address bits The bit selection bit is determined and can be dynamically modified by software. A configuration mail named SCID\_SEL is set in the system Register to determine the address selection bits, as shown in the table below. By default, [7: 6] address hashing is used for distribution, That is, two bits of address [7: 6] determine the corresponding shared cache number. The register address is 0x3FF00400 or 0x1fe00400.

#### Table 3- 3 SCID\_SEL address bit setting

| SCID_SEL | Address bit selection | SCID_SEL | Address bit selection |

|----------|-----------------------|----------|-----------------------|

| 4'h0     | 7: 6                  | 4'h8     | 23:22                 |

| 4'h1     | 9: 8                  | 4'h9     | 25:24                 |

| 4'h2     | 11:10                 | 4'ha     | 27:26                 |

| 4'h3     | 13:12                 | 4'hb     | 29:28                 |

| 4'h4     | 15:14                 | 4'hc     | 31:30                 |

| 4'h5     | 17:16                 | 4'hd     | 33:32                 |

| 4'h6     | 19:18                 | 4'he     | 35:34                 |

| 4'h7     | 21:20                 | 4'hf     | 37:36                 |

The default distribution of the internal 44-bit physical address of each node of Loongson 3A4000 processor is shown in the following table:

Access attribute

#### Table 3-4 44-bit physical address distribution in the node

Address range

destination

#### Page 29

8

#### Loongson 3A4000 processor register user manual

| addr [43:40] == 4'ha                                                      | Local node, uncache | HT0_LO  |

|---------------------------------------------------------------------------|---------------------|---------|

| addr [43:40] == 4'hb                                                      | Local node, uncache | HT0_HI  |

| addr [43:40] == 4'hc                                                      | Local node, uncache | SE      |

| addr [43:40] == 4'he                                                      | Local node, uncache | HT1_LO  |

| addr [43:40] == 4'hf                                                      | Local node, uncache | HT1_HI  |

| 0x10000000-0x1fffffff, 0x3ff00000-0x3ff0ffff (can be closed)              | Local node, uncache | MISC    |

| Mc interleave is 0, and not the above address                             | Local node, uncache | MC0     |

| Mc interleave is 1, and not the above address                             | Local node, uncache | MC1     |

| Scache interleave is 0 (address bit selection determined by scid_sel)     | Local node, cache   | Scache0 |

| Scache interleave is 1 (selection of address bits determined by scid_sel) | Local node, cache   | Scache1 |

| Scache interleave is 2 (address bit selection determined by scid_sel)     | Local node, cache   | Scache2 |

| Scache interleave is 3 (selection of address bits determined by scid_sel) | Local node, cache   | Scache3 |

3.3 Address routing distribution and configuration

The routing of Loongson 3A4000 is mainly realized through the system's two-level crossbar switch and IO-RING. The software can

The master port receives requests for routing configuration. Each master port has 8 address windows, which can be completed

Target routing in 8 address windows. Each address window is composed of three 64-bit registers BASE, MASK and MMAP,

BASE is aligned in K bytes; MASK adopts a format similar to the high bit of the netmask; the lower four bits of MMAP indicate the corresponding target

Slave port number, MMAP [4] means to allow instruction fetch, MMAP [5] means to allow block reading, MMAP [6] means to allow interleaving

Access is enabled, MMAP [7] means the window is enabled.

#### Table 3-5 The space access attributes corresponding to the MMAP field

| [7]           | [6]                                         | [5]        | [4]            |

|---------------|---------------------------------------------|------------|----------------|

| Window enable | Allow interleaved access to SCACHE / memory | Block read | Allow fetching |

Window hit formula: (IN\_ADDR & MASK) == BASE

Since Loongson 3 uses fixed routing by default, the configuration window is closed when the power is turned on.

System software is required to enable and configure it.

After the SCACHE / memory interleaving access configuration is enabled, the slave number is only valid when it is 0 or 4. 0 means route to

SCACHE, and SCID\_SEL decides how to interleave access in 4 SCACHEs. 4 means routing to memory, by

interleave\_bit determines how to interleave access between 2 MCs.

The address window conversion register is shown in the table below.

Table 3- 6 Address window register table

#### Page 30

9

| address     | ragistar                    | address     | register                    |

|-------------|-----------------------------|-------------|-----------------------------|

| 0x3ff0_2000 | register<br>CORE0_WIN0_BASE | 0x3ff0_2100 | register<br>CORE1_WIN0_BASE |

| 0x3ff0 2008 | CORE0 WIN1 BASE             | 0x3ff0 2108 | CORE1 WIN1 BASE             |

| 0x3ff0 2010 | CORE0 WIN2 BASE             | 0x3ff0 2110 | CORE1 WIN2 BASE             |

| 0x3ff0_2018 | CORE0_WIN3_BASE             | 0x3ff0_2118 | CORE1_WIN2_BASE             |

| 0x3ff0 2020 | CORE0 WIN4 BASE             | 0x3ff0 2120 | CORE1 WIN4 BASE             |

| 0x3ff0 2028 | CORE0 WIN5 BASE             | 0x3ff0 2128 | CORE1 WIN5 BASE             |

| 0x3ff0_2020 | CORE0_WIN6_BASE             | 0x3ff0 2130 | CORE1_WIN6_BASE             |

| 0x3ff0 2038 | CORE0 WIN7 BASE             | 0x3ff0 2138 | CORE1 WIN7 BASE             |

| 0x3ff0_2040 | CORE0_WIN0_MASK             | 0x3ff0 2140 | CORE1_WIN0_MASK             |

| 0x3ff0_2048 | CORE0_WIN1_MASK             | 0x3ff0_2148 | CORE1_WIN1_MASK             |

| 0x3ff0_2050 | CORE0 WIN2 MASK             | 0x3ff0_2150 | CORE1 WIN2 MASK             |

| 0x3ff0_2058 | CORE0_WIN2_MASK             | 0x3ff0_2158 | CORE1_WIN2_MASK             |

| 0x3ff0 2060 | CORE0 WIN4 MASK             | 0x3ff0 2160 | CORE1 WIN4 MASK             |

| 0x3ff0_2068 | CORE0_WIN4_MASK             | 0x3ff0_2168 | CORE1_WIN5_MASK             |

| 0x3ff0 2070 | CORE0_WIN5_MASK             | 0x3ff0_2170 | CORE1_WIN5_MASK             |

| —           |                             | -           |                             |

| 0x3ff0_2078 | CORE0_WIN7_MASK             | 0x3ff0_2178 | CORE1_WIN7_MASK             |

| 0x3ff0_2080 | CORE0_WIN0_MMAP             | 0x3ff0_2180 | CORE1_WIN0_MMAP             |

| 0x3ff0_2088 | CORE0_WIN1_MMAP             | 0x3ff0_2188 | CORE1_WIN1_MMAP             |

| 0x3ff0_2090 | CORE0_WIN2_MMAP             | 0x3ff0_2190 | CORE1_WIN2_MMAP             |

| 0x3ff0_2098 | CORE0_WIN3_MMAP             | 0x3ff0_2198 | CORE1_WIN3_MMAP             |

| 0x3ff0_20a0 | CORE0_WIN4_MMAP             | 0x3ff0_21a0 | CORE1_WIN4_MMAP             |