# Loongson 3A1000 processor user's manual Part i

Multicore processor architecture, register description and system software programming guide

V1.15

Sep 2015

Loongson technology co. LTD

自主决定命运,创新成就未来

# **Copyright statement**

The copyright of this document belongs to loongson technology co., LTD. All rights reserved. No company or individual may make public, reprint or otherwise distribute any portion of this document to a third party without written permission. Otherwise, will pursue its legal responsibility certainly.

#### disclaimer

This document only provides periodic information, and the content can be updated at any time according to the actual situation of the product without prior notice. The company shall not be liable for any direct or indirect loss caused by improper use of the documents.

#### Loongson technology co. LTD

Loongson Technology Corporation Limited Address: Loongson Industrial Park, Building No. 2, loongson Industrial Park, zhongguancun environmental science and technology demonstration Park, haidian district, Beijing Zhongguancun Environmental Protection Park, Haidian District, Beijing Tel: 010-62546668 Fax: 010-62600826

#### -Reading guide------

\_\_\_\_\_

Loongson 3A1000 processor user manual is divided into volume 1 and volume 2.

Loongson 3A1000 processor user's manual is divided into two parts. The first part (chapter  $1 \sim$  chapter 10) introduces loongson 3A1000 multi-core processor architecture and register description, and gives a detailed description of chip system architecture, functions and configuration of main modules, register list and bit domain. The second part (chapter 11 ~ chapter 16) is the system software programming guide, which introduces the common problems in the development of BIOS and operating system.

The second volume of loongson 3A1000 processor user manual introduces in detail the GS464 highperformance processor core adopted by loongson 3A1000 from the perspective of system software developers.

# **Revision history**

| Docun                                                    | Document update record |       | The<br>document<br>name:                                                                                                                                                                                                                                                         | Loongson 3A1000 processor<br>user's manual<br>- the days |                                       |  |

|----------------------------------------------------------|------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|---------------------------------------|--|

|                                                          |                        |       | The version<br>number                                                                                                                                                                                                                                                            | V1.15                                                    |                                       |  |

|                                                          |                        |       |                                                                                                                                                                                                                                                                                  | The<br>founders:                                         | Research and development center       |  |

|                                                          |                        |       |                                                                                                                                                                                                                                                                                  | Date of creation:                                        | 2015-09-11                            |  |

| Update                                                   | e history              |       |                                                                                                                                                                                                                                                                                  |                                                          |                                       |  |

| The<br>serialUpdated<br>dateThe<br>version<br>num<br>ber |                        |       |                                                                                                                                                                                                                                                                                  | Update<br>the<br>content                                 |                                       |  |

| 1                                                        | 2009-10-30             | V1.0  | Add<br>addro                                                                                                                                                                                                                                                                     |                                                          | R parameters;Fixed UART, SPI base     |  |

| 2                                                        | 2009-11-13             | V1.1  | Add                                                                                                                                                                                                                                                                              | the definition of PCI_                                   | CONFIG to the configuration pin       |  |

| 3                                                        | 2010-06-25             | V1.2  | The second part of the manual is added, including the configuration and use of interrupt, configuration and use of serial port, EJTAG debugging instructions, address window configuration conversion, system memory space distribution design and memory allocation of X system |                                                          |                                       |  |

| 4                                                        | 2010-06-29             | V1.3  | Modified the first chapter overview, the second chapter address distribution                                                                                                                                                                                                     |                                                          |                                       |  |

| 5                                                        | 2010-07-20             | V1.4  | Fixed some text errors in the HT configuration register                                                                                                                                                                                                                          |                                                          | he HT configuration register          |  |

| 6                                                        | 2010-07-28             | V1.5  | In section 10.5, Chip Config and Chip Sample register definitions are added                                                                                                                                                                                                      |                                                          | fig and Chip Sample register          |  |

| 7                                                        | 2010-12-17             | V1.6  | Revise the definition of DDR parameters                                                                                                                                                                                                                                          |                                                          |                                       |  |

| 8                                                        | 2011-11-24             | V1.7  | Modify the cover                                                                                                                                                                                                                                                                 |                                                          |                                       |  |

| 9                                                        | 2012-02-14             | V1.8  | Add                                                                                                                                                                                                                                                                              | CLKSEL setting rest                                      | rictions                              |  |

| 10                                                       | 2012-02-23             | V1.9  | Adde                                                                                                                                                                                                                                                                             | ed DDR configuration                                     | register interrupt vector description |  |

| 11                                                       | 2012-04-25             | V1.10 | Added details of the chip configuration register<br>Added details of HT diagnostic register                                                                                                                                                                                      |                                                          |                                       |  |

| 12                                                       | 2012-08-23             | V1.11 | Revise the DDR parameter definition<br>Added HT register definition supported by LS3A1000E                                                                                                                                                                                       |                                                          |                                       |  |

| 13                                                       | 2012-10-30             | V1.12 | Adde                                                                                                                                                                                                                                                                             | ed matrix handling reg                                   | gister supported by LS3A1000E         |  |

| 14                                                       | 2014-04-02             | V1.13 | According to the chip naming rules, the loongson 3A processor<br>was renamed loongson 3A1000 processor                                                                                                                                                                           |                                                          |                                       |  |

| 15                                                       | 2014-07-24             | V1.14 | Industrial level chip content added                                                                                                                                                                                                                                              |                                                          |                                       |  |

| 龙芯 | 3A1000 | 处理器用 | 户手册 | 目录 |

|----|--------|------|-----|----|

|----|--------|------|-----|----|

| 16 | 2015-09-11 | V1.15 | Fixed GPIO configuration register description |

|----|------------|-------|-----------------------------------------------|

|----|------------|-------|-----------------------------------------------|

V

# 目录

| Part 1 |                                                                                        | 错误!未定义书容 | 奁。  |

|--------|----------------------------------------------------------------------------------------|----------|-----|

| Multic | ore processor architecture, register description and system software programming guide |          | . 1 |

| Revisi | on history                                                                             |          | . 4 |

| 1      | overview                                                                               |          | . 2 |

| 2      | System configuration and control                                                       |          | . 0 |

| 4      | Level 2 Cache                                                                          |          | 27  |

| 5      | Matrix processing accelerator                                                          |          | 29  |

| 6 In   | terrupt and communication between processor cores                                      |          | 33  |

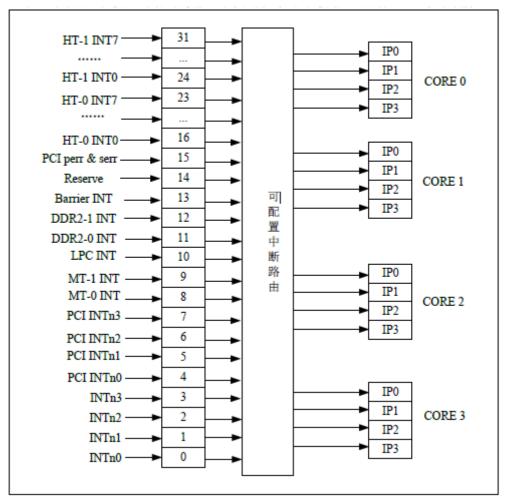

| 7      | I/O interrupt                                                                          |          | 36  |

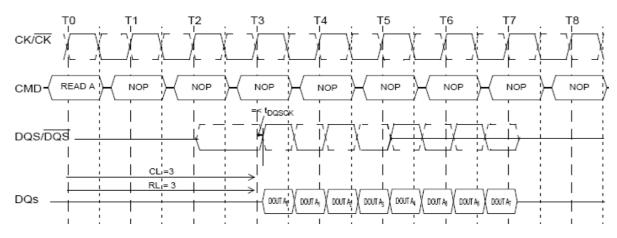

| 8      | Ddr2/3 SDRAM controller configuration                                                  |          | 36  |

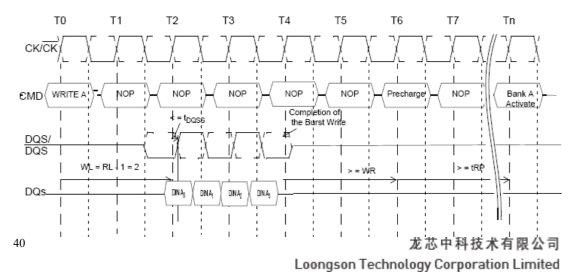

| 8      | 3 Ddr2/3 SDRAM write operation protocol                                                |          | 40  |

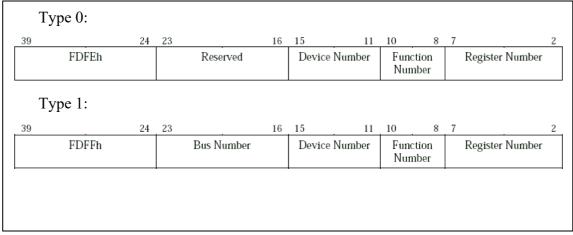

| 9      | HyperTransport controller                                                              |          | 95  |

| 1      | 0 Low speed IO controller configuration                                                |          | 125 |

| 1      | 3 EJTAG debugging                                                                      |          | 131 |

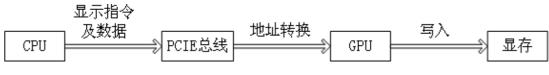

| 1      | 4 Configure the translation in the address window                                      |          | 138 |

| 1      | 5 System memory space distribution design                                              |          | 148 |

| 1      | 6 Memory allocation for system X                                                       | •••••    | 151 |

龙芯中科技术有限公司 Loongson Technology Corporation Limited

# The first part

Multi-core processor architecture, register description

龙芯中科技术有限公司 Loongson Technology Corporation Limited

# 1 overview

# 1. 1 Introduction to loongson series processors

The loongson processor mainly includes three series. Loongson 1 processor and its IP series are mainly for embedded applications, loongson 2 superstandard processor and its IP series are mainly for desktop applications, and loongson 3 multi-core processor series are mainly for server and high-performance machine applications. According to the application needs, part of the loongson 2 can also be oriented to part of the high-end embedded should With, part of low - end loongson 3 can also face part of the desktop application. The three series will develop in parallel.

Based on the scalable multi-core interconnect architecture, the loong chip 3 multi-core series integrates multiple high-performance processor cores and a large number of level-2 caches on a single chip, and interconnects multiple chips through high-speed I/O interfaces to form a larger system.

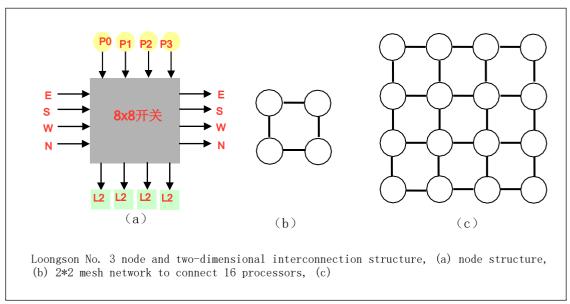

The retractable interconnection structure adopted by loongson 3 is shown in figure 1-1below.Loongson 3 and multi - chip system are adopted 2D mesh interconnection structure, in which each node is composed of 8\*8 cross-switches, each cross-switch connects four processor cores and four second-level caches, and interconnects with other nodes in the four directions of east (E), south (N), west (W) and north (N).Therefore, a 2\*2 mesh can connect 16 processor cores, and a 4\*4 mesh can connect 64 processor cores.

Figure 1-1 loongson 3 system structure

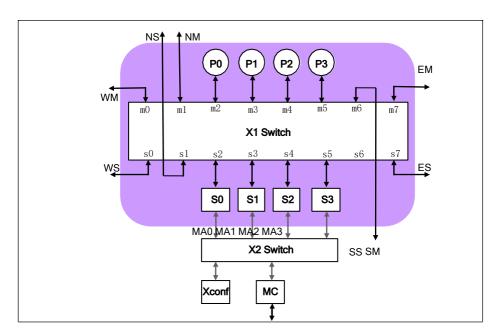

The node structure of loongson 3 is shown in figure 1-2 below. Each node has two levels

of AXI cross-switches connected to the processor, a secondary Cache, a memory controller, 2 龙芯中科技术有限公司

Loongson Technology Corporation Limited

and an IO controller. The first level AXI cross Switch (called the X1 Switch) connects the processor to the secondary Cache. The second level cross Switch (called the X2 Switch) connects the second level Cache to the memory controller.

Figure 1-2 structure of loongson node3

At most 8\*8 X1 crossovers are connected to four GS464 processor cores via four Master ports at each node

(P0, P1, P2, P3 in the figure), connect the four interleave second-level Cache blocks (S0, S1, S2, S3 in the figure) with four Slave ports, and connect other nodes or IO nodes (EM/ES, SM/SS, WM/WS, NM/NS in the figure) with four Master/Slave ports in the east, south, west, and north directions.

The X2 cross-switch connects four secondary caches through four Master ports, at least one Slave port to a memory controller, and at least one Slave port to a cross-switch configuration module (Xconf) to configure the local node's X1 and X2 address Windows.You can also connect more memory controllers and IO ports as needed.

The interconnection system in loongson 3 only defines the upper layer protocol, which does not specify the implementation of the transport protocol. Therefore, the interconnection between nodes can be realized either through the on-chip network or through the I/O control link to realize multi-chip interconnection. In a 4-node 16-core system, for example, it can be composed of either 4 4-core chips or 2 8-core chips

A nuclear chip, or a 16-core chip composed of four nodes based on a single chip.Because the physical implementation of the interconnected system is transparent to the software,

The above three configurations of the system can run the same operating system.

#### 1. 2 Introduction to loongson 3A1000

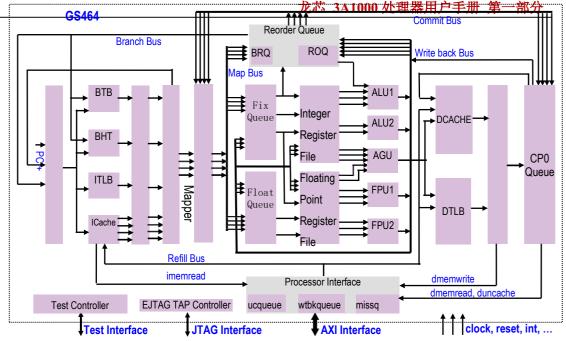

The loongson 3A1000 is the first product of the loongson no. 3 multi-core processor series. It is a single-node processor with 4 cores.

Four 64-bit quad-emission superscalar GS464 high-performance processor cores are integrated on the chip.

4 MB split Shared second-level Cache(composed of 4 individual modules, each with a capacity of 1MB);

Maintain Cache consistency for multi-core and I/O DMA access through directory protocols;

Two 64 bit 400MHz ddr2/3 controllers are integrated on the chip.

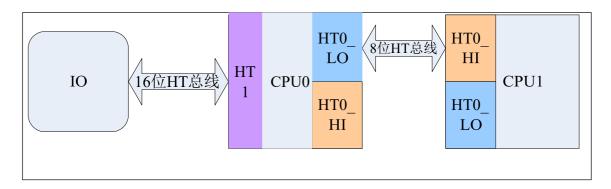

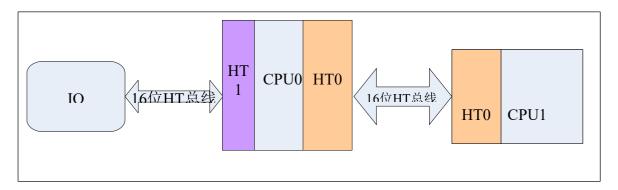

Two 16-bit 800MHz HyperTransport controllers are integrated on the chip;

Each 16-bit HT port is split into two 8-way HT ports for use.

32-bit 100MHz PCIX/66MHz PCI;

1 LPC, 2 UART, 1 SPI and 16 GPIO interfaces are integrated on the chip.

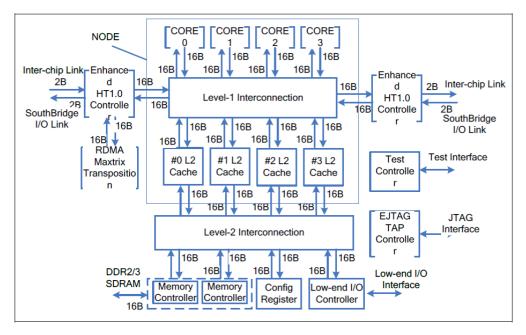

The overall architecture of loongson 3A1000 chip is based on two-level interconnection, as shown in figure 1-3 below.

Figure 1-3 chip structure of Godson 3a10 1

The first level of interconnect USES 6x6 cross-switches to connect four cpus (as Master devices), four secondary Cache modules (as Slave devices), and two IO ports (one Master and one Slave for each port).Each IO port connected by the level 1 interconnect switch is connected to a 16-bit HT controller, and each 16-bit HT port can also be used as two 8-bit HT ports.The HT controller is connected to a level 1 interconnect switch by a DMA controller, which is responsible for the DMA control of IO and the maintenance of inter-chip consistency.The loongson 3's DMA controller can also be configured to prefetch and matrix transpose or shift.

The second level interconnection USES a 5x4 cross-switch to connect 4 secondary Cache modules (as the main device) and 2 DDR2

Memory controller, low speed and high speed I/O (including PCI, LPC, SPI, etc.) and the control register module inside the chip.The above two level interconnect switches all adopt the data channel separated by read and write. The data channel width is 128bit and

works at the same place

The same frequency is used to provide high-speed on-chip data transmission.

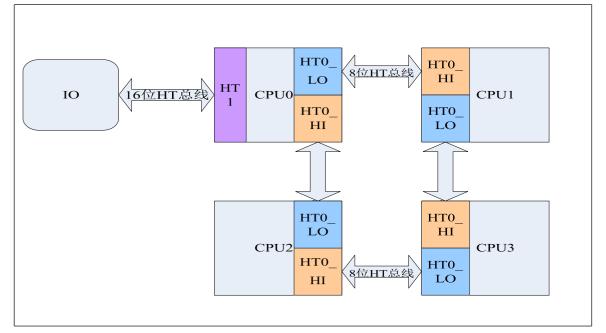

Based on the loongson no. 3 extensible interconnection architecture, 4 pieces of fourcore loongson 3A1000 can be connected via HT port to form 4 chips

16 - core SMP structure.

#### 1. 3 Loongson 3A1000 commercial grade and industrial grade chips Loongson 3A1000 chip has two kinds of industrial grade and commercial grade. Its main

features are as follows:

| configuration                     | Commercial grade | industrial-grade |

|-----------------------------------|------------------|------------------|

| Working temperature               | 0 °C ~ 70 °C     | - 40 °C ~ 85 °C  |

| Whether screening                 | -                | Square root      |

| Quality consistency test          | -                | Square root      |

| Quality consistency test standard | -                | GB 4937-1995     |

As with most semiconductor devices, the failure rate of the loongson 3A chip conforms to the bathtub curve model. In order to ensure a more long-term, stable and reliable operation, and to adapt to the more stringent environmental temperature requirements, loongson 3A industrial-grade chip was selected for reliability, so as to eliminate the early failure of the chip. This reliability screening is 100% trial, through which the chips are screened for industrial-grade applications

The main contents of loongson 3A screening test are as follows:

| Screening program                                 | Methods and conditions (summary)                                                  | requireme<br>nts |

|---------------------------------------------------|-----------------------------------------------------------------------------------|------------------|

| 1, visual inspection                              | Clear identification, no contamination, no oxidation of welding ball, chip intact | 100%             |

| 2. Stable baking                                  | 125 °C for 24 h                                                                   | 100%             |

| 3. The temperature changes rapidly                | 10 cycles at maximum and minimum storage temperatures                             | 100%             |

| 4. Serial number                                  |                                                                                   | 100%             |

| 5, intermediate (before the old) electrical test  | The normal temperature                                                            | 100%             |

| 6, aging                                          | TC = 85 °C, 160 h                                                                 | 100%             |

| 7. Intermediate (after aging) electrical test     | The normal temperature                                                            | 100%             |

| 8. Percentage of defective products allowed (PDA) | PDA≤5%, normal temperature, when 5% < PDA≤10%, can be heavy                       | All batch        |

| To calculate                                      | New submissions, but only once                                                    |                  |

| 9. Terminal electrical test                       | Three temperature, record all test data                                           | 100%             |

| 10. External visual inspection                    | Clear identification, no contamination, no oxidation of welding ball, chip intact | 100%             |

# 2 System configuration and control

#### 2.1 Chip working mode

According to the structure of the composing system, loongson 3A1000 has two working modes:

Single chip mode. The system only integrates one loongson 3A1000, which is a symmetric multiprocessor system (SMP).

Multi-chip interconnection model. The system consists of 2 or 4 loongson 3A1000, which is interlinked through the HT port of loongson 3A1000. It is a non-uniform memory multi-processor system (cc-numa)

Control pin instructions

The control pins of loongson 3A1000 include DO\_TEST, ICCC\_EN, NODE\_ID[1:0], CLKSEL[15:0], and PCI\_CONFIG. Table 2-1 control pin description

| signal           | Pull<br>up and<br>down | role                                                                             |

|------------------|------------------------|----------------------------------------------------------------------------------|

| DO_TEST          | On the<br>pull         | 1 'b1 represents the functional mode                                             |

|                  | Pull                   | 1 'b0 represents the test mode                                                   |

|                  |                        | 1 'b1 represents the consistent interconnection mode of multiple chips           |

| ICCC_EN          | The<br>drop-<br>down   | 1 'b0 stands for single chip mode                                                |

| NODE_ID<br>[1:0] |                        | Represents the processor number in the multichip consistent interconnection mode |

|                  |                        | Power on clock control                                                           |

|                  |                        | HT clock<br>control                                                              |

| 龙芯 3A1000 处理器用户手册 第一语 |

|-----------------------|

|-----------------------|

|               | signal      | role                                                                                                                                                                                                                                                                |

|---------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKSEL [15:0] | CLKSEL [15] | 1 'b1 indicates the use of internal reference voltage<br>1 'b0 indicates external reference voltage                                                                                                                                                                 |

|               | CLKSEL [14] | 1 'b1 means HT PLL USES differential clock input<br>1 'b0 means HT PLL USES normal clock input                                                                                                                                                                      |

|               | CLKSEL [12] | <ul> <li>2 'b00 represents the PHY clock of 1.6GHZ/1</li> <li>2 'b01 represents the PHY clock of 3.2GHZ/2</li> <li>2 'b10 represents the PHY clock. It is an ordinary input clock</li> <li>2 'b11 represents PHY clock and is a differential input clock</li> </ul> |

|               | CLKSEL [10] | 2 'b00 represents HT controller clock 200MHz<br>2 'b01 represents HT controller clock 400MHz                                                                                                                                                                        |

2 'b1x means that HT controller clock is an ordinary

|                   | input clock MEM clock control                               |                                                      |  |  |  |

|-------------------|-------------------------------------------------------------|------------------------------------------------------|--|--|--|

|                   | signal                                                      | role                                                 |  |  |  |

|                   |                                                             | 5 'b11111 means that MEM clock directly              |  |  |  |

|                   |                                                             | adopts memclk. In other cases, MEM clock is          |  |  |  |

|                   | 01.1/051                                                    | memclk*(clksel[8:5]+30)/(clksel[9]+3)                |  |  |  |

|                   | CLKSEL<br>[will]                                            | Note:                                                |  |  |  |

|                   |                                                             | Memclk *(clksel[8:5]+30) must be 600MHz~             |  |  |  |

|                   |                                                             | 1.36ghz memclk must be 10~40MHz                      |  |  |  |

|                   |                                                             | CORE clock<br>control                                |  |  |  |

|                   | signal                                                      | role                                                 |  |  |  |

|                   |                                                             | 5 'b11111 means that the CORE clock                  |  |  |  |

|                   |                                                             | directly adopts sysclk. In other cases, the          |  |  |  |

|                   |                                                             | CORE clock is                                        |  |  |  |

|                   | CLKSEL<br>[Wednesday]                                       | sysclk*(clksel[3:0]+30)/(clksel[4]+1).               |  |  |  |

|                   |                                                             | Note:                                                |  |  |  |

|                   |                                                             | Sysclk *(clksel[3:0]+30) must be 600MHz~ 1.36ghz     |  |  |  |

|                   | IO configuration contro                                     |                                                      |  |  |  |

|                   | 7HT control signal pin<br>control bit 1* 6:5 PCIX           |                                                      |  |  |  |

|                   | selection *                                                 |                                                      |  |  |  |

|                   | 4PCIX bus mode selection                                    |                                                      |  |  |  |

|                   | 3PCI main device mode                                       |                                                      |  |  |  |

|                   | 2 the system is started from the PCI space                  |                                                      |  |  |  |

|                   | 1 use external PCI me                                       |                                                      |  |  |  |

| PCI_CONFIG [away] | 0HT control signal pin                                      | voltage control bit 0*                               |  |  |  |

|                   | $\begin{array}{c c} Note * \\ \hline 6 & - & 4 \end{array}$ | PCIX bus pattern                                     |  |  |  |

|                   | 0 - 0                                                       | PCI 33/66                                            |  |  |  |

|                   | 0 1 1<br>1 0 1                                              | PCI - 66 X<br>PCI - 10 - X                           |  |  |  |

|                   |                                                             | PCI - 133 X                                          |  |  |  |

|                   | 7 0 HT c                                                    | ontrols the pin voltage of the signal. These signals |  |  |  |

|                   | inclu                                                       | de HT_8x2, HT_Mode,                                  |  |  |  |

|                   |                                                             | Powerok, HT_Rstn, HT_Ldt_Stopn, HT_Ldt_Reqn.         |  |  |  |

|                   |                                                             | 0 0 1.8 v<br>0 1 Reserved                            |  |  |  |

|                   |                                                             |                                                      |  |  |  |

|                   | 1 1 3.3 v                                                   |                                                      |  |  |  |

# 2.2 The Cache consistency

The loongson 3A1000 is maintained by the hardware for the Cache consistency between the processor and the I/O accessed through the HT port, but the hardware does not maintain the Cache consistency of the I/O devices accessed through PCI into the system.At the time of driver development, the software is required to maintain Cache consistency for DMA (Direct Memory Access) transfers to devices accessed through PCI.

#### 2.3 Physical address space distribution at the system node level

The system physical address distribution of the loongson 3 series processor adopts globally accessible hierarchical addressing design to ensure

System development extension compatibility. The overall system physical address width is 48 bits. According to the height of the address, the whole address is empty

It is evenly distributed among 16 nodes, that is, each node is allocated with a 44-bit address space.

The godson 3A1000 adopts a single-node 4-core configuration, so the corresponding addresses of the DDR memory controller, HT bus and PCI bus integrated by the godson 3A1000 chip are all contained in the 44-bit address space from 0x0 (inclusive) to  $0x1000\_0000\_0000$  (not inclusive). Please refer to the following relevant sections for the address distribution of each device.

Table 2-2 node-level system global address distribution

| Node number | Address [47:44] | The starting address | End address       |

|-------------|-----------------|----------------------|-------------------|

|             |                 | 0 x0000_0000_0000    | 0 x1000_0000_0000 |

| 1           | 1               | 0 x1000_0000_0000    | 0 x2000_0000_0000 |

| 2           | 2               | 0 x2000_0000_0000    | 0 x3000_0000_0000 |

| 3           | 3               | 0 x3000_0000_0000    | 0 x4000_0000_0000 |

| 4           | 4               | 0 x4000_0000_0000    | 0 x5000_0000_0000 |

| 5           | 5               | 0 x5000_0000_0000    | 0 x6000_0000_0000 |

| 6           | 6               | 0 x6000_0000_0000    | 0 x7000_0000_0000 |

| 7           | 7               | 0 x7000_0000_0000    | 0 x8000_0000_0000 |

| 8           | 8               | 0 x8000_0000_0000    | 0 x9000_0000_0000 |

| 9  | 9    | 0 x9000_0000_0000 | 0 xa000_0000_0000   |

|----|------|-------------------|---------------------|

| 10 | 0 xa | 0 xa000_0000_0000 | 0 xb000_0000_0000   |

| 11 | 0 xb | 0 xb000_0000_0000 | 0 xc000_0000_0000   |

| 12 | 0 xc | 0 xc000_0000_0000 | 0 xd000_0000_0000   |

| 13 | 0 xd | 0 xd000_0000_0000 | 0 xe000_0000_0000   |

| 14 | 0 xe | 0 xe000_0000_0000 | 0 xf000_0000_0000   |

| 15 | 0 xf | 0 xf000_0000_0000 | 0 x1_0000_0000_0000 |

Within each node, the 44-bit address space is further evenly distributed among up to eight possible devices connected within the node. The low 43-bit address is owned by four 2-level Cache modules, and the high 43-bit address is further determined by the [43:42] of the address.

Bits are distributed to devices connected to four directional ports.Depending on the chip and system configuration, if there is no slave device connected to a port, the corresponding address space is reserved address space and access is not allowed.

| equip<br>ment | Address [43:41] | The initial address within the node | End of node address |

|---------------|-----------------|-------------------------------------|---------------------|

| Level 2 Cache | 0,1,2,3         | 0 x000_0000_0000                    | 0 x800_0000_0000    |

| In the east   | 4               | 0 x800_0000_0000                    | 0 xa00_0000_0000    |

| south         | 5               | 0 xa00_0000_0000                    | 0 xc00_0000_0000    |

| In the west   | 6               | 0 xc00_0000_0000                    | 0 xe00_0000_0000    |

| north         | 7               | 0 xe00_0000_0000                    | 0 x1000_0000_0000   |

Table 2-3 address distribution within nodes

For example, the base address of the east end port device of node 0 is 0x0800\_0000\_0000, the base address of the east end port device of node 1 is 0x1800\_0000\_0000, and so on.

Unlike the directional port mapping, the loongson 3A1000 can determine the cross-addressing mode of the secondary Cache based on the actual access behavior of the application. The four level-2 Cache modules in the node correspond to a total of 43 address Spaces, and the address space corresponding to each level-2 module is determined according to a certain two selection bits of the address bit, which can be dynamically configured and modified by the software. A configuration register named SCID\_SEL is set in the system to determine the address selection bit, as shown in the following table. By default, it is distributed in a [6:5] status hash, where the address [6:5] determines the corresponding level 2 Cache number. The register address is 0x3FF00400.

| SCID_SEL | Address bit selection | SCID_SEL | Address bit selection |

|----------|-----------------------|----------|-----------------------|

| 4'h0     | 6: 5                  | 4'h8     | 23:22                 |

| 4'h1     | 9: 8                  | 4'h9     | 25:24                 |

| 4'h2     | 11:10                 | 4'ha     | 27:26                 |

| 4'h3     | 13:12                 | 4'hb     | 29:28                 |

| 4'h4     | 15:14                 | 4'hc     | 31:30                 |

| 4'h5     | 17:16                 | 4'hd     | 33:32                 |

| 4'h6     | 19:18                 | 4'he     | 35:34                 |

# 2.4 Address routing distribution and configuration

The routing of loongson 3A1000 is mainly realized through the two-stage crossover switch of the system. A level 1 cross switch can configure the routing of requests received by each Master port. Each Master port has 8 address Windows, which can complete the target routing of 8 address Windows. Each address window consists of three 64-bit registers, BASE, MASK and MMAP. BASE is aligned with K bytes. The MASK used a format similar to the network MASK with a high position of 1. The lower three bits of MMAP represent the number of the target Slave port, MMAP[4] means the allowed fetch-pointing, MMAP[5] means the allowed block reading, and MMAP[7] means the enabled window.

Window hit formula :(IN\_ADDR & MASK) == BASE

Because the loongson 3 adopts fixed route by default, the configuration window is closed when it is powered on and started, so the system software is required to enable it to be configured when it is in use.

The address window conversion register is shown in the following table.

Table 2-5 register table of level 1 crossover switch address window

| address      | register        | address      | register        |

|--------------|-----------------|--------------|-----------------|

| 0 x3ff0_2000 | CORE0_WIN0_BASE | 0 x3ff0_2100 | CORE1_WIN0_BASE |

| 0 x3ff0_2008 | CORE0_WIN1_BASE | 0 x3ff0_2108 | CORE1_WIN1_BASE |

| 0 x3ff0_2010 | CORE0_WIN2_BASE | 0 x3ff0_2110 | CORE1_WIN2_BASE |

| 0 x3ff0_2018 | CORE0_WIN3_BASE | 0 x3ff0_2118 | CORE1_WIN3_BASE |

| 0 x3ff0_2020 | CORE0_WIN4_BASE | 0 x3ff0_2120 | CORE1_WIN4_BASE |

| 0 x3ff0_2028 | CORE0_WIN5_BASE | 0 x3ff0_2128 | CORE1_WIN5_BASE |

| 0 x3ff0_2030 | CORE0_WIN6_BASE | 0 x3ff0_2130 | CORE1_WIN6_BASE |

| 0 x3ff0_2038 | CORE0_WIN7_BASE | 0 x3ff0_2138 | CORE1_WIN7_BASE |

| 0 x3ff0_2040 | CORE0_WIN0_MASK | 0 x3ff0_2140 | CORE1_WIN0_MASK |

| 0 x3ff0_2048 | CORE0_WIN1_MASK | 0 x3ff0_2148 | CORE1_WIN1_MASK |

| 0 x3ff0_2050 | CORE0_WIN2_MASK | 0 x3ff0_2150 | CORE1_WIN2_MASK |

| 0 x3ff0_2058 | CORE0_WIN3_MASK | 0 x3ff0_2158 | CORE1_WIN3_MASK |

| 0 x3ff0_2060 | CORE0_WIN4_MASK | 0 x3ff0_2160 | CORE1_WIN4_MASK |

| 0 x3ff0_2068 | CORE0_WIN5_MASK | 0 x3ff0_2168 | CORE1_WIN5_MASK |

| 0 x3ff0_2070 | CORE0_WIN6_MASK | 0 x3ff0_2170 | CORE1_WIN6_MASK |

| 0 x3ff0_2078 | CORE0_WIN7_MASK | 0 x3ff0_2178 | CORE1_WIN7_MASK |

| 0 x3ff0_2080 | CORE0_WIN0_MMAP | 0 x3ff0_2180 | CORE1_WIN0_MMAP |

| 0 x3ff0_2088 | CORE0_WIN1_MMAP | 0 x3ff0_2188 | CORE1_WIN1_MMAP |

| 0 x3ff0_2090 | CORE0_WIN2_MMAP | 0 x3ff0_2190 | CORE1_WIN2_MMAP |

| 0 x3ff0_2098 | CORE0_WIN3_MMAP | 0 x3ff0_2198 | CORE1_WIN3_MMAP |

|--------------|-----------------|--------------|-----------------|

| 0 x3ff0_20a0 | CORE0_WIN4_MMAP | 0 x3ff0_21a0 | CORE1_WIN4_MMAP |

| 0 x3ff0_20a8 | CORE0_WIN5_MMAP | 0 x3ff0_21a8 | CORE1_WIN5_MMAP |

| 0 x3ff0_20b0 | CORE0_WIN6_MMAP | 0 x3ff0_21b0 | CORE1_WIN6_MMAP |

| 0 x3ff0_20b8 | CORE0_WIN7_MMAP | 0 x3ff0_21b8 | CORE1_WIN7_MMAP |

| 0 x3ff0_2200 | CORE2_WIN0_BASE | 0 x3ff0_2300 | CORE3_WIN0_BASE |

| 0 x3ff0_2208 | CORE2_WIN1_BASE | 0 x3ff0_2308 | CORE3_WIN1_BASE |

| 0 x3ff0_2210 | CORE2_WIN2_BASE | 0 x3ff0_2310 | CORE3_WIN2_BASE |

| 0 x3ff0_2218 | CORE2_WIN3_BASE | 0 x3ff0_2318 | CORE3_WIN3_BASE |

| 0 x3ff0_2220 | CORE2_WIN4_BASE | 0 x3ff0_2320 | CORE3_WIN4_BASE |

| 0 x3ff0_2228 | CORE2_WIN5_BASE | 0 x3ff0_2328 | CORE3_WIN5_BASE |

| 0 x3ff0_2230 | CORE2_WIN6_BASE | 0 x3ff0_2330 | CORE3_WIN6_BASE |

| 0 x3ff0_2238 | CORE2_WIN7_BASE | 0 x3ff0_2338 | CORE3_WIN7_BASE |

| 0 x3ff0_2240 | CORE2_WIN0_MASK | 0 x3ff0_2340 | CORE3_WIN0_MASK |

| 0 x3ff0_2248 | CORE2_WIN1_MASK | 0 x3ff0_2348 | CORE3_WIN1_MASK |

| 0 x3ff0_2250 | CORE2_WIN2_MASK | 0 x3ff0_2350 | CORE3_WIN2_MASK |

| 0 x3ff0_2258 | CORE2_WIN3_MASK | 0 x3ff0_2358 | CORE3_WIN3_MASK |

| 0 x3ff0_2260 | CORE2_WIN4_MASK | 0 x3ff0_2360 | CORE3_WIN4_MASK |

| 0 x3ff0_2268 | CORE2_WIN5_MASK | 0 x3ff0_2368 | CORE3_WIN5_MASK |

| 0 x3ff0_2270 | CORE2_WIN6_MASK | 0 x3ff0_2370 | CORE3_WIN6_MASK |

| 0 x3ff0_2278 | CORE2_WIN7_MASK | 0 x3ff0_2378 | CORE3_WIN7_MASK |

| 0 x3ff0_2280 | CORE2_WIN0_MMAP | 0 x3ff0_2380 | CORE3_WIN0_MMAP |

| 0 x3ff0_2288 | CORE2_WIN1_MMAP | 0 x3ff0_2388 | CORE3_WIN1_MMAP |

| 0 x3ff0_2290 | CORE2_WIN2_MMAP | 0 x3ff0_2390 | CORE3_WIN2_MMAP |

| 0 x3ff0_2298 | CORE2_WIN3_MMAP | 0 x3ff0_2398 | CORE3_WIN3_MMAP |

| 0 x3ff0_22a0 | CORE2_WIN4_MMAP | 0 x3ff0_23a0 | CORE3_WIN4_MMAP |

| 0 x3ff0_22a8 | CORE2_WIN5_MMAP | 0 x3ff0_23a8 | CORE3_WIN5_MMAP |

| 0 x3ff0_22b0 | CORE2_WIN6_MMAP | 0 x3ff0_23b0 | CORE3_WIN6_MMAP |

| 0 x3ff0_22b8 | CORE2_WIN7_MMAP | 0 x3ff0_23b8 | CORE3_WIN7_MMAP |

| 0 x3ff0_2400 | EAST_WIN0_BASE  | 0 x3ff0_2500 | SOUTH_WIN0_BASE |

| 0 x3ff0_2408 | EAST_WIN1_BASE  | 0 x3ff0_2508 | SOUTH_WIN1_BASE |

| 0 x3ff0_2410 | EAST_WIN2_BASE  | 0 x3ff0_2510 | SOUTH_WIN2_BASE |

| 0 x3ff0_2418 | EAST_WIN3_BASE  | 0 x3ff0_2518 | SOUTH_WIN3_BASE |

|              |                 |              |                 |

| 0 x3ff0_2420EAST_WIN4_BASE0 x3ff0_2520SOUTH_WIN4_BASE0 x3ff0_2428EAST_WIN5_BASE0 x3ff0_2528SOUTH_WIN5_BASE0 x3ff0_2430EAST_WIN6_BASE0 x3ff0_2530SOUTH_WIN6_BASE0 x3ff0_2440EAST_WIN7_BASE0 x3ff0_2540SOUTH_WIN1_MASK0 x3ff0_2440EAST_WIN2_MASK0 x3ff0_2540SOUTH_WIN1_MASK0 x3ff0_2443EAST_WIN2_MASK0 x3ff0_2550SOUTH_WIN1_MASK0 x3ff0_2450EAST_WIN2_MASK0 x3ff0_2550SOUTH_WIN3_MASK0 x3ff0_2452EAST_WIN5_MASK0 x3ff0_2560SOUTH_WIN4_MASK0 x3ff0_2454EAST_WIN5_MASK0 x3ff0_2560SOUTH_WIN5_MASK0 x3ff0_2470EAST_WIN5_MASK0 x3ff0_2570SOUTH_WIN5_MASK0 x3ff0_24710EAST_WIN7_MASK0 x3ff0_2578SOUTH_WIN7_MASK0 x3ff0_2478EAST_WIN7_MASK0 x3ff0_2580SOUTH_WIN7_MAPA0 x3ff0_2480EAST_WIN3_MMAP0 x3ff0_2598SOUTH_WIN3_MMAP0 x3ff0_2490EAST_WIN3_MMAP0 x3ff0_2598SOUTH_WIN3_MMAP0 x3ff0_2491EAST_WIN5_MMAP0 x3ff0_2580SOUTH_WIN4_MAPA0 x3ff0_2492EAST_WIN5_MMAP0 x3ff0_2580SOUTH_WIN5_MMAP0 x3ff0_2448EAST_WIN6_MAP0 x3ff0_2580SOUTH_WIN5_MMAP0 x3ff0_2440EAST_WIN6_MAP0 x3ff0_2580SOUTH_WIN5_MAPA0 x3ff0_2440EAST_WIN5_MAP0 x3ff0_2580SOUTH_WIN5_MAPA0 x3ff0_2440EAST_WIN7_MAP0 x3ff0_2580SOUTH_WIN5_MAPA0 x3ff0_2440WEST_WIN6_BASE0 x3ff0_2780NORTH_WI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |                |              |                 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------|--------------|-----------------|

| 0 x3ft0_2430         EAST_WIN6_BASE         0 x3ft0_2530         SOUTH_WIN6_BASE           0 x3ft0_2438         EAST_WIN7_BASE         0 x3ft0_2538         SOUTH_WIN7_BASE           0 x3ft0_2440         EAST_WIN0_MASK         0 x3ft0_2548         SOUTH_WIN0_MASK           0 x3ft0_2448         EAST_WIN1_MASK         0 x3ft0_2548         SOUTH_WIN1_MASK           0 x3ft0_2450         EAST_WIN2_MASK         0 x3ft0_2550         SOUTH_WIN2_MASK           0 x3ft0_2458         EAST_WIN3_MASK         0 x3ft0_2558         SOUTH_WIN3_MASK           0 x3ft0_2460         EAST_WIN5_MASK         0 x3ft0_2568         SOUTH_WIN5_MASK           0 x3ft0_2460         EAST_WIN6_MASK         0 x3ft0_2568         SOUTH_WIN5_MASK           0 x3ft0_2470         EAST_WIN6_MASK         0 x3ft0_2570         SOUTH_WIN6_MASK           0 x3ft0_2470         EAST_WIN7_MASK         0 x3ft0_2580         SOUTH_WIN7_MASK           0 x3ft0_2480         EAST_WIN2_MMAP         0 x3ft0_2580         SOUTH_WIN3_MMAP           0 x3ft0_2480         EAST_WIN3_MARP         0 x3ft0_2580         SOUTH_WIN3_MMAP           0 x3ft0_2480         EAST_WIN3_MMAP         0 x3ft0_2580         SOUTH_WIN3_MMAP           0 x3ft0_2480         EAST_WIN6_MMAP         0 x3ft0_2580         SOUTH_WIN4_MMAP           0 x3ft0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 x3ff0_2420 | EAST_WIN4_BASE | 0 x3ff0_2520 | SOUTH_WIN4_BASE |

| 0 x3ff0 2438         EAST_WIN7_BASE         0 x3ff0 2538         SOUTH_WIN7_BASE           0 x3ff0 2440         EAST_WIN0_MASK         0 x3ff0 2540         SOUTH_WIN0_MASK           0 x3ff0 2440         EAST_WIN1_MASK         0 x3ff0 2550         SOUTH_WIN2_MASK           0 x3ff0 2450         EAST_WIN2_MASK         0 x3ff0 2550         SOUTH_WIN2_MASK           0 x3ff0 2458         EAST_WIN3_MASK         0 x3ff0 2550         SOUTH_WIN3_MASK           0 x3ff0 2460         EAST_WIN5_MASK         0 x3ff0 2560         SOUTH_WIN4_MASK           0 x3ff0 2460         EAST_WIN5_MASK         0 x3ff0 2570         SOUTH_WIN5_MASK           0 x3ff0 2470         EAST_WIN6_MASK         0 x3ff0 2570         SOUTH_WIN7_MASK           0 x3ff0 2470         EAST_WIN6_MASK         0 x3ff0 2578         SOUTH_WIN7_MASK           0 x3ff0 2480         EAST_WIN0_MMAP         0 x3ff0 2580         SOUTH_WIN1_MMAP           0 x3ff0 2480         EAST_WIN3_MMAP         0 x3ff0 2598         SOUTH_WIN3_MMAP           0 x3ff0 2480         EAST_WIN3_MAP         0 x3ff0 2588         SOUTH_WIN3_MAP           0 x3ff0 2488         EAST_WIN4_MMAP         0 x3ff0 2598         SOUTH_WIN3_MAP           0 x3ff0 2488         EAST_WIN5_MMAP         0 x3ff0 2508         SOUTH_WIN4_MAP           0 x3ff0 248                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 x3ff0_2428 | EAST_WIN5_BASE | 0 x3ff0_2528 | SOUTH_WIN5_BASE |

| 0 x3ff0 2440         EAST_WIN0_MASK         0 x3ff0_2540         SOUTH_WIN0_MASK           0 x3ff0_2448         EAST_WIN1_MASK         0 x3ff0_2548         SOUTH_WIN1_MASK           0 x3ff0_2450         EAST_WIN2_MASK         0 x3ff0_2550         SOUTH_WIN2_MASK           0 x3ff0_2458         EAST_WIN3_MASK         0 x3ff0_2558         SOUTH_WIN3_MASK           0 x3ff0_2460         EAST_WIN4_MASK         0 x3ff0_2568         SOUTH_WIN4_MASK           0 x3ff0_2460         EAST_WIN5_MASK         0 x3ff0_2570         SOUTH_WIN5_MASK           0 x3ff0_2470         EAST_WIN6_MASK         0 x3ff0_2570         SOUTH_WIN7_MASK           0 x3ff0_2470         EAST_WIN6_MASK         0 x3ff0_2570         SOUTH_WIN7_MASK           0 x3ff0_2470         EAST_WIN6_MASK         0 x3ff0_2580         SOUTH_WIN7_MASK           0 x3ff0_2480         EAST_WIN2_MMAP         0 x3ff0_2590         SOUTH_WIN2_MMAP           0 x3ff0_2490         EAST_WIN3_MMAP         0 x3ff0_2590         SOUTH_WIN3_MMAP           0 x3ff0_2448         EAST_WIN4_MMAP         0 x3ff0_2548         SOUTH_WIN4_MMAP           0 x3ff0_2448         EAST_WIN5_MMAP         0 x3ff0_2548         SOUTH_WIN4_MAP           0 x3ff0_2448         EAST_WIN5_MMAP         0 x3ff0_2548         SOUTH_WIN4_MAP           0 x3ff0_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 x3ff0_2430 | EAST_WIN6_BASE | 0 x3ff0_2530 | SOUTH_WIN6_BASE |

| 0 x3ff0_2448EAST_WIN1_MASK0 x3ff0_2548SOUTH_WIN1_MIASK0 x3ff0_2450EAST_WIN2_MASK0 x3ff0_2550SOUTH_WIN2_MASK0 x3ff0_2460EAST_WIN3_MASK0 x3ff0_2558SOUTH_WIN3_MASK0 x3ff0_2460EAST_WIN4_MASK0 x3ff0_2568SOUTH_WIN4_MASK0 x3ff0_2470EAST_WIN5_MASK0 x3ff0_2570SOUTH_WIN5_MASK0 x3ff0_24770EAST_WIN6_MASK0 x3ff0_2578SOUTH_WIN7_MASK0 x3ff0_2478EAST_WIN7_MASK0 x3ff0_2578SOUTH_WIN7_MASK0 x3ff0_2480EAST_WIN7_MASK0 x3ff0_2588SOUTH_WIN7_MASK0 x3ff0_2480EAST_WIN2_MMAP0 x3ff0_2598SOUTH_WIN3_MMAP0 x3ff0_2490EAST_WIN3_MMAP0 x3ff0_2598SOUTH_WIN3_MMAP0 x3ff0_2490EAST_WIN3_MMAP0 x3ff0_2598SOUTH_WIN4_MAP0 x3ff0_2440EAST_WIN5_MMAP0 x3ff0_2500SOUTH_WIN4_MAP0 x3ff0_2440EAST_WIN6_MMAP0 x3ff0_2508SOUTH_WIN6_MMAP0 x3ff0_2440EAST_WIN6_MMAP0 x3ff0_2508SOUTH_WIN6_MMAP0 x3ff0_2440EAST_WIN6_MMAP0 x3ff0_2508SOUTH_WIN6_MMAP0 x3ff0_2460WEST_WIN6_MAP0 x3ff0_2700NORTH_WIN6_MAP0 x3ff0_2600WEST_WIN1_BASE0 x3ff0_2710NORTH_WIN1_BASE0 x3ff0_2610WEST_WIN2_BASE0 x3ff0_2718NORTH_WIN3_BASE0 x3ff0_2620WEST_WIN5_BASE0 x3ff0_2720NORTH_WIN3_BASE0 x3ff0_2620WEST_WIN5_BASE0 x3ff0_2738NORTH_WIN5_BASE0 x3ff0_2638WEST_WIN5_BASE0 x3ff0_2748NORTH_W                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 x3ff0_2438 | EAST_WIN7_BASE | 0 x3ff0_2538 | SOUTH_WIN7_BASE |

| 0 x3ff0_2450EAST_WIN2_MASK0 x3ff0_2550SOUTH_WIN2_MASK0 x3ff0_2458EAST_WIN3_MASK0 x3ff0_2558SOUTH_WIN3_MASK0 x3ff0_2460EAST_WIN4_MASK0 x3ff0_2560SOUTH_WIN4_MASK0 x3ff0_2470EAST_WIN5_MASK0 x3ff0_2568SOUTH_WIN5_MASK0 x3ff0_24770EAST_WIN6_MASK0 x3ff0_2578SOUTH_WIN6_MASK0 x3ff0_2478EAST_WIN7_MASK0 x3ff0_2578SOUTH_WIN7_MASK0 x3ff0_2478EAST_WIN1_MAP0 x3ff0_2580SOUTH_WIN7_MASK0 x3ff0_2480EAST_WIN2_MMAP0 x3ff0_2590SOUTH_WIN1_MMAP0 x3ff0_2490EAST_WIN2_MMAP0 x3ff0_2590SOUTH_WIN3_MMAP0 x3ff0_2498EAST_WIN3_MMAP0 x3ff0_2598SOUTH_WIN3_MMAP0 x3ff0_2440EAST_WIN5_MMAP0 x3ff0_2548SOUTH_WIN4_MMAP0 x3ff0_2440EAST_WIN5_MMAP0 x3ff0_2548SOUTH_WIN5_MMAP0 x3ff0_2440EAST_WIN6_MMAP0 x3ff0_2548SOUTH_WIN6_MMAP0 x3ff0_2440EAST_WIN6_MMAP0 x3ff0_2548SOUTH_WIN6_MMAP0 x3ff0_2440EAST_WIN6_MMAP0 x3ff0_2548SOUTH_WIN6_MMAP0 x3ff0_2440EAST_WIN1_BASE0 x3ff0_2700NORTH_WIN6_MASE0 x3ff0_2610WEST_WIN1_BASE0 x3ff0_2710NORTH_WIN1_BASE0 x3ff0_2620WEST_WIN3_BASE0 x3ff0_2728NORTH_WIN3_BASE0 x3ff0_2628WEST_WIN4_BASE0 x3ff0_2728NORTH_WIN5_BASE0 x3ff0_2630WEST_WIN6_BASE0 x3ff0_2740NORTH_WIN7_BASE0 x3ff0_2640WEST_WIN6_BASE0 x3ff0_2748NORTH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 x3ff0_2440 | EAST_WIN0_MASK | 0 x3ff0_2540 | SOUTH_WIN0_MASK |

| 0 x3ff0_2458EAST_WIN3_MASK0 x3ff0_2558SOUTH_WIN3_MASK0 x3ff0_2460EAST_WIN4_MASK0 x3ff0_2560SOUTH_WIN4_MASK0 x3ff0_2468EAST_WIN5_MASK0 x3ff0_2568SOUTH_WIN5_MASK0 x3ff0_2470EAST_WIN6_MASK0 x3ff0_2570SOUTH_WIN6_MASK0 x3ff0_2478EAST_WIN7_MASK0 x3ff0_2578SOUTH_WIN7_MASK0 x3ff0_2480EAST_WIN0_MMAP0 x3ff0_2580SOUTH_WIN7_MASK0 x3ff0_2480EAST_WIN1_MMAP0 x3ff0_2588SOUTH_WIN2_MMAP0 x3ff0_2490EAST_WIN2_MMAP0 x3ff0_2590SOUTH_WIN2_MMAP0 x3ff0_2490EAST_WIN3_MMAP0 x3ff0_2590SOUTH_WIN3_MMAP0 x3ff0_2488EAST_WIN3_MMAP0 x3ff0_2588SOUTH_WIN3_MMAP0 x3ff0_2480EAST_WIN5_MMAP0 x3ff0_2588SOUTH_WIN4_MMAP0 x3ff0_2488EAST_WIN5_MMAP0 x3ff0_2588SOUTH_WIN5_MMAP0 x3ff0_2488EAST_WIN5_MMAP0 x3ff0_2588SOUTH_WIN5_MMAP0 x3ff0_2488EAST_WIN7_MMAP0 x3ff0_2588SOUTH_WIN6_MMAP0 x3ff0_2600WEST_WIN6_MMAP0 x3ff0_2700NORTH_WIN6_MAP0 x3ff0_2610WEST_WIN2_BASE0 x3ff0_2708NORTH_WIN1_BASE0 x3ff0_2610WEST_WIN3_BASE0 x3ff0_2718NORTH_WIN3_BASE0 x3ff0_2628WEST_WIN3_BASE0 x3ff0_2728NORTH_WIN4_BASE0 x3ff0_2628WEST_WIN5_BASE0 x3ff0_2738NORTH_WIN5_BASE0 x3ff0_2640WEST_WIN6_BASE0 x3ff0_2748NORTH_WIN7_BASE0 x3ff0_2648WEST_WIN1_MASK0 x3ff0_2750NORTH_                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 x3ff0_2448 | EAST_WIN1_MASK | 0 x3ff0_2548 | SOUTH_WIN1_MASK |

| 0 x3ff0_2460EAST_WIN4_MASK0 x3ff0_2560SOUTH_WIN4_MASK0 x3ff0_2468EAST_WIN5_MASK0 x3ff0_2568SOUTH_WIN5_MASK0 x3ff0_2470EAST_WIN6_MASK0 x3ff0_2570SOUTH_WIN6_MASK0 x3ff0_2478EAST_WIN7_MASK0 x3ff0_2578SOUTH_WIN7_MASK0 x3ff0_2480EAST_WIN1_MMAP0 x3ff0_2580SOUTH_WIN7_MASK0 x3ff0_2480EAST_WIN1_MMAP0 x3ff0_2580SOUTH_WIN2_MMAP0 x3ff0_2488EAST_WIN1_MMAP0 x3ff0_2580SOUTH_WIN2_MMAP0 x3ff0_2490EAST_WIN2_MMAP0 x3ff0_2580SOUTH_WIN2_MMAP0 x3ff0_2490EAST_WIN3_MMAP0 x3ff0_2580SOUTH_WIN3_MMAP0 x3ff0_2490EAST_WIN4_MMAP0 x3ff0_2580SOUTH_WIN3_MMAP0 x3ff0_2490EAST_WIN5_MMAP0 x3ff0_2580SOUTH_WIN5_MMAP0 x3ff0_2480EAST_WIN5_MMAP0 x3ff0_2580SOUTH_WIN5_MMAP0 x3ff0_2440EAST_WIN5_MMAP0 x3ff0_2580SOUTH_WIN5_MMAP0 x3ff0_2440EAST_WIN5_MMAP0 x3ff0_2580SOUTH_WIN5_MMAP0 x3ff0_2440EAST_WIN6_MMAP0 x3ff0_2580SOUTH_WIN5_MMAP0 x3ff0_2640WEST_WIN6_BASE0 x3ff0_2700NORTH_WIN0_BASE0 x3ff0_2610WEST_WIN1_BASE0 x3ff0_2718NORTH_WIN1_BASE0 x3ff0_2628WEST_WIN3_BASE0 x3ff0_2728NORTH_WIN4_BASE0 x3ff0_2628WEST_WIN6_BASE0 x3ff0_2730NORTH_WIN5_BASE0 x3ff0_2630WEST_WIN6_BASE0 x3ff0_2740NORTH_WIN7_BASE0 x3ff0_2640WEST_WIN6_BASE0 x3ff0_2748NORTH                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 x3ff0_2450 | EAST_WIN2_MASK | 0 x3ff0_2550 | SOUTH_WIN2_MASK |

| 0 x3ff0_2468 EAST_WIN5_MASK 0 x3ff0_2568 SOUTH_WIN5_MASK<br>0 x3ff0_2470 EAST_WIN6_MASK 0 x3ff0_2570 SOUTH_WIN6_MASK<br>0 x3ff0_2478 EAST_WIN7_MASK 0 x3ff0_2578 SOUTH_WIN7_MASK<br>0 x3ff0_2480 EAST_WIN0_MMAP 0 x3ff0_2580 SOUTH_WIN0_MMAP<br>0 x3ff0_2488 EAST_WIN1_MMAP 0 x3ff0_2588 SOUTH_WIN1_MMAP<br>0 x3ff0_2490 EAST_WIN2_MMAP 0 x3ff0_2590 SOUTH_WIN2_MMAP<br>0 x3ff0_2498 EAST_WIN3_MMAP 0 x3ff0_2598 SOUTH_WIN3_MMAP<br>0 x3ff0_2440 EAST_WIN5_MMAP 0 x3ff0_2508 SOUTH_WIN3_MMAP<br>0 x3ff0_2440 EAST_WIN5_MMAP 0 x3ff0_2508 SOUTH_WIN5_MMAP<br>0 x3ff0_2440 EAST_WIN5_MMAP 0 x3ff0_2508 SOUTH_WIN5_MMAP<br>0 x3ff0_2440 EAST_WIN6_MMAP 0 x3ff0_2508 SOUTH_WIN5_MMAP<br>0 x3ff0_2440 EAST_WIN6_MMAP 0 x3ff0_2508 SOUTH_WIN5_MMAP<br>0 x3ff0_2460 EAST_WIN6_MMAP 0 x3ff0_2508 SOUTH_WIN5_MMAP<br>0 x3ff0_2600 WEST_WIN6_MAP 0 x3ff0_2700 NORTH_WIN6_MMAP<br>0 x3ff0_2600 WEST_WIN1_BASE 0 x3ff0_2700 NORTH_WIN1_BASE<br>0 x3ff0_2610 WEST_WIN2_BASE 0 x3ff0_2710 NORTH_WIN2_BASE<br>0 x3ff0_2618 WEST_WIN3_BASE 0 x3ff0_2710 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN4_BASE 0 x3ff0_2720 NORTH_WIN4_BASE<br>0 x3ff0_2620 WEST_WIN4_BASE 0 x3ff0_2720 NORTH_WIN4_BASE<br>0 x3ff0_2628 WEST_WIN5_BASE 0 x3ff0_2728 NORTH_WIN5_BASE<br>0 x3ff0_2630 WEST_WIN6_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2640 WEST_WIN6_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN7_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2648 WEST_WIN7_BASE 0 x3ff0_2748 NORTH_WIN6_BASE<br>0 x3ff0_2648 WEST_WIN1_MASK 0 x3ff0_2748 NORTH_WIN1_MASK<br>0 x3ff0_2648 WEST_WIN1_MASK 0 x3ff0_2748 NORTH_WIN2_MASK<br>0 x3ff0_2648 WEST_WIN3_MASK 0 x3ff0_2748 NORTH_WIN3_MASK | 0 x3ff0_2458 | EAST_WIN3_MASK | 0 x3ff0_2558 | SOUTH_WIN3_MASK |

| 0 x3ff0_2470         EAST_WIN6_MASK         0 x3ff0_2570         SOUTH_WIN6_MASK           0 x3ff0_2478         EAST_WIN7_MASK         0 x3ff0_2578         SOUTH_WIN7_MASK           0 x3ff0_2480         EAST_WIN0_MMAP         0 x3ff0_2580         SOUTH_WIN0_MMAP           0 x3ff0_2480         EAST_WIN1_MMAP         0 x3ff0_2588         SOUTH_WIN1_MMAP           0 x3ff0_2490         EAST_WIN2_MMAP         0 x3ff0_2590         SOUTH_WIN2_MMAP           0 x3ff0_2490         EAST_WIN3_MMAP         0 x3ff0_2590         SOUTH_WIN3_MMAP           0 x3ff0_2490         EAST_WIN4_MMAP         0 x3ff0_2590         SOUTH_WIN3_MMAP           0 x3ff0_2490         EAST_WIN4_MMAP         0 x3ff0_2590         SOUTH_WIN4_MMAP           0 x3ff0_2440         EAST_WIN5_MMAP         0 x3ff0_2588         SOUTH_WIN5_MMAP           0 x3ff0_2440         EAST_WIN6_MMAP         0 x3ff0_2580         SOUTH_WIN5_MMAP           0 x3ff0_2440         EAST_WIN6_MMAP         0 x3ff0_2580         SOUTH_WIN5_MMAP           0 x3ff0_2440         EAST_WIN6_MMAP         0 x3ff0_2580         SOUTH_WIN5_MMAP           0 x3ff0_2600         WEST_WIN6_MAP         0 x3ff0_2700         NORTH_WIN7_MAP           0 x3ff0_2608         WEST_WIN2_BASE         0 x3ff0_2700         NORTH_WIN1_BASE           0 x3ff0_2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 x3ff0_2460 | EAST_WIN4_MASK | 0 x3ff0_2560 | SOUTH_WIN4_MASK |

| 0 x3ff0_2478         EAST_WIN7_MASK         0 x3ff0_2578         SOUTH_WIN7_MASK           0 x3ff0_2480         EAST_WIN0_MMAP         0 x3ff0_2580         SOUTH_WIN0_MMAP           0 x3ff0_2488         EAST_WIN1_MMAP         0 x3ff0_2588         SOUTH_WIN1_MMAP           0 x3ff0_2490         EAST_WIN2_MMAP         0 x3ff0_2590         SOUTH_WIN2_MMAP           0 x3ff0_2498         EAST_WIN3_MMAP         0 x3ff0_2598         SOUTH_WIN3_MMAP           0 x3ff0_2440         EAST_WIN4_MMAP         0 x3ff0_2540         SOUTH_WIN4_MMAP           0 x3ff0_2448         EAST_WIN5_MMAP         0 x3ff0_2540         SOUTH_WIN4_MMAP           0 x3ff0_2448         EAST_WIN6_MMAP         0 x3ff0_2540         SOUTH_WIN6_MMAP           0 x3ff0_2440         EAST_WIN6_MMAP         0 x3ff0_2540         SOUTH_WIN6_MMAP           0 x3ff0_2440         EAST_WIN6_MMAP         0 x3ff0_2540         SOUTH_WIN6_MAP           0 x3ff0_2600         WEST_WIN0_BASE         0 x3ff0_2700         NORTH_WIN1_BASE           0 x3ff0_2610         WEST_WIN1_BASE         0 x3ff0_2710         NORTH_WIN1_BASE           0 x3ff0_26218         WEST_WIN3_BASE         0 x3ff0_2720         NORTH_WIN3_BASE           0 x3ff0_2628         WEST_WIN5_BASE         0 x3ff0_2730         NORTH_WIN4_BASE           0 x3ff0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0 x3ff0_2468 | EAST_WIN5_MASK | 0 x3ff0_2568 | SOUTH_WIN5_MASK |

| 0 x3ff0_2480 EAST_WIN0_MMAP 0 x3ff0_2580 SOUTH_WIN0_MMAP<br>0 x3ff0_2488 EAST_WIN1_MMAP 0 x3ff0_2588 SOUTH_WIN1_MMAP<br>0 x3ff0_2490 EAST_WIN2_MMAP 0 x3ff0_2590 SOUTH_WIN2_MMAP<br>0 x3ff0_24a0 EAST_WIN3_MMAP 0 x3ff0_2598 SOUTH_WIN3_MMAP<br>0 x3ff0_24a0 EAST_WIN5_MMAP 0 x3ff0_25a0 SOUTH_WIN4_MMAP<br>0 x3ff0_24a8 EAST_WIN5_MMAP 0 x3ff0_25a8 SOUTH_WIN5_MMAP<br>0 x3ff0_24b0 EAST_WIN5_MMAP 0 x3ff0_25b8 SOUTH_WIN5_MMAP<br>0 x3ff0_24b0 EAST_WIN6_MMAP 0 x3ff0_25b8 SOUTH_WIN6_MMAP<br>0 x3ff0_24b0 EAST_WIN7_MMAP 0 x3ff0_25b8 SOUTH_WIN7_MMAP<br>0 x3ff0_2600 WEST_WIN0_BASE 0 x3ff0_2700 NORTH_WIN0_BASE<br>0 x3ff0_2600 WEST_WIN1_BASE 0 x3ff0_2708 NORTH_WIN1_BASE<br>0 x3ff0_2610 WEST_WIN2_BASE 0 x3ff0_2718 NORTH_WIN2_BASE<br>0 x3ff0_2618 WEST_WIN3_BASE 0 x3ff0_2718 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN5_BASE 0 x3ff0_2720 NORTH_WIN4_BASE<br>0 x3ff0_2628 WEST_WIN5_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN5_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN6_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN6_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN7_BASE 0 x3ff0_2738 NORTH_WIN6_BASE<br>0 x3ff0_2638 WEST_WIN7_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2648 WEST_WIN7_BASE 0 x3ff0_2748 NORTH_WIN5_BASE<br>0 x3ff0_2648 WEST_WIN7_BASE 0 x3ff0_2748 NORTH_WIN6_BASE<br>0 x3ff0_2648 WEST_WIN3_MASK 0 x3ff0_2748 NORTH_WIN3_MASK<br>0 x3ff0_2648 WEST_WIN3_MASK 0 x3ff0_2748 NORTH_WIN3_MASK                                                                                                                                                                                                                                                                                                                                                                        | 0 x3ff0_2470 | EAST_WIN6_MASK | 0 x3ff0_2570 | SOUTH_WIN6_MASK |

| 0 x3ff0_2488 EAST_WIN1_MMAP 0 x3ff0_2588 SOUTH_WIN1_MMAP<br>0 x3ff0_2490 EAST_WIN2_MMAP 0 x3ff0_2590 SOUTH_WIN2_MMAP<br>0 x3ff0_2498 EAST_WIN3_MMAP 0 x3ff0_2598 SOUTH_WIN3_MMAP<br>0 x3ff0_24a0 EAST_WIN4_MMAP 0 x3ff0_25a0 SOUTH_WIN4_MMAP<br>0 x3ff0_24a8 EAST_WIN5_MMAP 0 x3ff0_25a8 SOUTH_WIN5_MMAP<br>0 x3ff0_24b0 EAST_WIN6_MMAP 0 x3ff0_25b8 SOUTH_WIN5_MMAP<br>0 x3ff0_24b8 EAST_WIN7_MMAP 0 x3ff0_25b8 SOUTH_WIN6_MMAP<br>0 x3ff0_2600 WEST_WIN0_BASE 0 x3ff0_2700 NORTH_WIN0_BASE<br>0 x3ff0_2608 WEST_WIN1_BASE 0 x3ff0_2708 NORTH_WIN1_BASE<br>0 x3ff0_2610 WEST_WIN2_BASE 0 x3ff0_2710 NORTH_WIN2_BASE<br>0 x3ff0_2618 WEST_WIN3_BASE 0 x3ff0_2718 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN5_BASE 0 x3ff0_2720 NORTH_WIN4_BASE<br>0 x3ff0_2620 WEST_WIN5_BASE 0 x3ff0_2728 NORTH_WIN5_BASE<br>0 x3ff0_2630 WEST_WIN5_BASE 0 x3ff0_2730 NORTH_WIN4_BASE<br>0 x3ff0_2630 WEST_WIN5_BASE 0 x3ff0_2730 NORTH_WIN5_BASE<br>0 x3ff0_2630 WEST_WIN6_BASE 0 x3ff0_2730 NORTH_WIN5_BASE<br>0 x3ff0_2630 WEST_WIN6_BASE 0 x3ff0_2730 NORTH_WIN5_BASE<br>0 x3ff0_2630 WEST_WIN6_BASE 0 x3ff0_2730 NORTH_WIN5_BASE<br>0 x3ff0_2640 WEST_WIN6_BASE 0 x3ff0_2730 NORTH_WIN6_BASE<br>0 x3ff0_2640 WEST_WIN7_BASE 0 x3ff0_2740 NORTH_WIN7_BASE<br>0 x3ff0_2648 WEST_WIN1_MASK 0 x3ff0_2748 NORTH_WIN1_MASK<br>0 x3ff0_2650 WEST_WIN3_MASK 0 x3ff0_2750 NORTH_WIN3_MASK                                                                                                                                                                                    | 0 x3ff0_2478 | EAST_WIN7_MASK | 0 x3ff0_2578 | SOUTH_WIN7_MASK |

| 0 x3ff0_2490EAST_WIN2_MMAP0 x3ff0_2590SOUTH_WIN2_MMAP0 x3ff0_2498EAST_WIN3_MMAP0 x3ff0_2598SOUTH_WIN3_MMAP0 x3ff0_24a0EAST_WIN4_MMAP0 x3ff0_25a0SOUTH_WIN4_MMAP0 x3ff0_24a8EAST_WIN5_MMAP0 x3ff0_25a8SOUTH_WIN5_MMAP0 x3ff0_24b0EAST_WIN6_MMAP0 x3ff0_25b0SOUTH_WIN6_MMAP0 x3ff0_24b0EAST_WIN6_MMAP0 x3ff0_25b0SOUTH_WIN6_MMAP0 x3ff0_24b8EAST_WIN7_MMAP0 x3ff0_25b8SOUTH_WIN6_MMAP0 x3ff0_2600WEST_WIN0_BASE0 x3ff0_2700NORTH_WIN0_BASE0 x3ff0_2608WEST_WIN1_BASE0 x3ff0_2708NORTH_WIN1_BASE0 x3ff0_2610WEST_WIN2_BASE0 x3ff0_2710NORTH_WIN3_BASE0 x3ff0_2618WEST_WIN3_BASE0 x3ff0_2718NORTH_WIN3_BASE0 x3ff0_2628WEST_WIN5_BASE0 x3ff0_2720NORTH_WIN4_BASE0 x3ff0_2630WEST_WIN5_BASE0 x3ff0_2730NORTH_WIN5_BASE0 x3ff0_2640WEST_WIN7_BASE0 x3ff0_2740NORTH_WIN1_BASE0 x3ff0_2640WEST_WIN1_MASK0 x3ff0_2748NORTH_WIN1_MASK0 x3ff0_2650WEST_WIN3_MASK0 x3ff0_2758NORTH_WIN3_MASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0 x3ff0_2480 | EAST_WIN0_MMAP | 0 x3ff0_2580 | SOUTH_WIN0_MMAP |

| 0 x3ff0_2498 EAST_WIN3_MMAP 0 x3ff0_2598 SOUTH_WIN3_MMAP<br>0 x3ff0_24a0 EAST_WIN4_MMAP 0 x3ff0_25a0 SOUTH_WIN4_MMAP<br>0 x3ff0_24a8 EAST_WIN5_MMAP 0 x3ff0_25a8 SOUTH_WIN5_MMAP<br>0 x3ff0_24b0 EAST_WIN6_MMAP 0 x3ff0_25b0 SOUTH_WIN6_MMAP<br>0 x3ff0_24b8 EAST_WIN7_MMAP 0 x3ff0_25b8 SOUTH_WIN7_MMAP<br>0 x3ff0_2600 WEST_WIN0_BASE 0 x3ff0_2700 NORTH_WIN0_BASE<br>0 x3ff0_2608 WEST_WIN1_BASE 0 x3ff0_2708 NORTH_WIN1_BASE<br>0 x3ff0_2610 WEST_WIN2_BASE 0 x3ff0_2710 NORTH_WIN2_BASE<br>0 x3ff0_2610 WEST_WIN3_BASE 0 x3ff0_2718 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN4_BASE 0 x3ff0_2718 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN5_BASE 0 x3ff0_2720 NORTH_WIN4_BASE<br>0 x3ff0_2628 WEST_WIN5_BASE 0 x3ff0_2728 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN5_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN5_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2640 WEST_WIN6_BASE 0 x3ff0_2740 NORTH_WIN6_BASE<br>0 x3ff0_2648 WEST_WIN7_BASE 0 x3ff0_2748 NORTH_WIN1_BASE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 x3ff0_2488 | EAST_WIN1_MMAP | 0 x3ff0_2588 | SOUTH_WIN1_MMAP |

| 0 x3ff0_24a0 EAST_WIN4_MMAP 0 x3ff0_25a0 SOUTH_WIN4_MMAP<br>0 x3ff0_24a8 EAST_WIN5_MMAP 0 x3ff0_25a8 SOUTH_WIN5_MMAP<br>0 x3ff0_24b0 EAST_WIN6_MMAP 0 x3ff0_25b0 SOUTH_WIN6_MMAP<br>0 x3ff0_24b8 EAST_WIN7_MMAP 0 x3ff0_25b8 SOUTH_WIN7_MMAP<br>0 x3ff0_2600 WEST_WIN0_BASE 0 x3ff0_2700 NORTH_WIN0_BASE<br>0 x3ff0_2608 WEST_WIN1_BASE 0 x3ff0_2708 NORTH_WIN1_BASE<br>0 x3ff0_2610 WEST_WIN2_BASE 0 x3ff0_2710 NORTH_WIN2_BASE<br>0 x3ff0_2618 WEST_WIN3_BASE 0 x3ff0_2718 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN4_BASE 0 x3ff0_2720 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN4_BASE 0 x3ff0_2720 NORTH_WIN4_BASE<br>0 x3ff0_2628 WEST_WIN5_BASE 0 x3ff0_2728 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN5_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN6_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2640 WEST_WIN6_BASE 0 x3ff0_2740 NORTH_WIN7_BASE<br>0 x3ff0_2640 WEST_WIN6_BASE 0 x3ff0_2740 NORTH_WIN7_BASE<br>0 x3ff0_2648 WEST_WIN1_MASK 0 x3ff0_2748 NORTH_WIN1_MASK<br>0 x3ff0_2658 WEST_WIN2_MASK 0 x3ff0_2758 NORTH_WIN1_MASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0 x3ff0_2490 | EAST_WIN2_MMAP | 0 x3ff0_2590 | SOUTH_WIN2_MMAP |

| 0 x3ff0_24a8 EAST_WIN5_MMAP 0 x3ff0_25a8 SOUTH_WIN5_MMAP<br>0 x3ff0_24b0 EAST_WIN6_MMAP 0 x3ff0_25b0 SOUTH_WIN6_MMAP<br>0 x3ff0_24b8 EAST_WIN7_MMAP 0 x3ff0_25b8 SOUTH_WIN7_MMAP<br>0 x3ff0_2600 WEST_WIN0_BASE 0 x3ff0_2700 NORTH_WIN0_BASE<br>0 x3ff0_2608 WEST_WIN1_BASE 0 x3ff0_2708 NORTH_WIN1_BASE<br>0 x3ff0_2610 WEST_WIN2_BASE 0 x3ff0_2710 NORTH_WIN2_BASE<br>0 x3ff0_2618 WEST_WIN3_BASE 0 x3ff0_2718 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN4_BASE 0 x3ff0_2720 NORTH_WIN3_BASE<br>0 x3ff0_2620 WEST_WIN5_BASE 0 x3ff0_2728 NORTH_WIN3_BASE<br>0 x3ff0_2638 WEST_WIN5_BASE 0 x3ff0_2728 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN5_BASE 0 x3ff0_2738 NORTH_WIN5_BASE<br>0 x3ff0_2638 WEST_WIN6_BASE 0 x3ff0_2738 NORTH_WIN6_BASE<br>0 x3ff0_2640 WEST_WIN7_BASE 0 x3ff0_2740 NORTH_WIN6_BASE<br>0 x3ff0_2640 WEST_WIN1_MASK 0 x3ff0_2748 NORTH_WIN1_MASK<br>0 x3ff0_2648 WEST_WIN1_MASK 0 x3ff0_2748 NORTH_WIN1_MASK<br>0 x3ff0_2658 WEST_WIN3_MASK 0 x3ff0_2758 NORTH_WIN3_MASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 0 x3ff0_2498 | EAST_WIN3_MMAP | 0 x3ff0_2598 | SOUTH_WIN3_MMAP |

| 0 x3ff0_24b0EAST_WIN6_MMAP0 x3ff0_25b0SOUTH_WIN6_MMAP0 x3ff0_24b8EAST_WIN7_MMAP0 x3ff0_25b8SOUTH_WIN7_MMAP0 x3ff0_2600WEST_WIN0_BASE0 x3ff0_2700NORTH_WIN0_BASE0 x3ff0_2608WEST_WIN1_BASE0 x3ff0_2708NORTH_WIN1_BASE0 x3ff0_2610WEST_WIN2_BASE0 x3ff0_2710NORTH_WIN2_BASE0 x3ff0_2618WEST_WIN3_BASE0 x3ff0_27118NORTH_WIN3_BASE0 x3ff0_2620WEST_WIN4_BASE0 x3ff0_2720NORTH_WIN3_BASE0 x3ff0_2628WEST_WIN5_BASE0 x3ff0_2728NORTH_WIN5_BASE0 x3ff0_2630WEST_WIN6_BASE0 x3ff0_2730NORTH_WIN6_BASE0 x3ff0_2638WEST_WIN6_BASE0 x3ff0_2738NORTH_WIN7_BASE0 x3ff0_2640WEST_WIN0_MASK0 x3ff0_2748NORTH_WIN1_MASK0 x3ff0_2650WEST_WIN3_MASK0 x3ff0_2758NORTH_WIN3_MASK0 x3ff0_2658WEST_WIN3_MASK0 x3ff0_2758NORTH_WIN3_MASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0 x3ff0_24a0 | EAST_WIN4_MMAP | 0 x3ff0_25a0 | SOUTH_WIN4_MMAP |