# **Loongson 1C300 Processor User Manual**

Version 1.0

April, 2014 Loongson Technology Corporation Limited

### **Reading Guide**

*Loongson 1C300 Processor User's Manual* mainly introduces the architecture and register of Loongson 1C300. For more information about LS232 high-performance processor core integrated by Loongson 1C300, please refer to *Loongson LS232 Processor User Manual*. Loongson 1C300 is hereinafter referred to as Loongson 1C.

# **Revision history**

| Date          | Edit       | Version | Change                                                                                                                                                     |

|---------------|------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Mar. 14, 2013 | R&D Centre | 0.0.1   | First draft                                                                                                                                                |

| Jun. 16, 2013 | R&D Centre | 0.0.2   |                                                                                                                                                            |

| Mar. 29, 2013 | R&D Centre | 0.0.3   | Supplement the description of DWT and interrupt configuration register; revise the description of modules such as CAMIF, UART and OTG.                     |

| Apr. 15, 2013 | R&D Centre | 0.1     | Address space revision                                                                                                                                     |

| Apr. 26, 2013 | R&D Centre | 0.2     |                                                                                                                                                            |

| Feb. 12, 2014 | R&D Centre | 0.3     | Modify and typeset                                                                                                                                         |

| Feb. 28, 2014 | R&D Centre | 0.9     | Modify 1C2 changes after revision                                                                                                                          |

| Apr. 21, 2014 | R&D Centre | 1.0     | Add the descriptions on pull-up/pull-down in the pin<br>Add the description of SRAM pin and revise some errors.<br>Chip name is updated as Loongson 1C 300 |

|               |            |         |                                                                                                                                                            |

### Content

| 1 Overview                                            |      |

|-------------------------------------------------------|------|

| 1.1 System Structure Chart                            | 10   |

| 1.2 Main Functions of the Chip                        | 10   |

| 1.2.1 Processor core                                  | 10   |

| 1.2.2 SDRAM Controller                                | 11   |

| 1.2.3 SRAM/NOR FLASH Controller                       | 11   |

| 1.2.4 NAND Controller                                 | 11   |

| 1.2.5 Clock generator                                 | 11   |

| 1.2.6 I <sup>2</sup> S controller                     |      |

| 1.2.7 AC97 controller                                 |      |

| 1.2.8 LCD controller                                  |      |

| 1.2.9 Camera interface                                |      |

| 1.2.10 MAC controller                                 |      |

| 1.2.11 USB2.0 controller                              |      |

| 1.2.12 SPI controller                                 |      |

| 1.2.13 I <sup>2</sup> C controller                    | 12   |

| 1.2.14 UART controller                                |      |

| 1.2.15 GPIO                                           |      |

| 1.2.16 PWM controller                                 |      |

| 1.2.17 RTC                                            |      |

| 1.2.18 CAN controller                                 |      |

| 1.2.19 SDIO controller                                |      |

| 1.2.20 ADC controller                                 |      |

| 2 Definition of Pin                                   |      |

| 2.1 Agreement                                         |      |

| 2.2 LCD Interface                                     |      |

|                                                       |      |

| 2.3 SDRAM Interface                                   |      |

| 2.4 SRAM/NOR Flash Interface                          |      |

| 2.5 I2S Interface                                     |      |

| 2.6 I 2C Interface                                    |      |

| 2.7 UART Interface                                    |      |

| 2.8 PWM Interface                                     |      |

| 2.9 ADC Interface                                     |      |

| 2.10 SPI Interface                                    |      |

| 2.11 EJTAG Interface                                  |      |

| 2.12 CAMERA Interface                                 |      |

| 2.13NAND Interface.                                   |      |

| 2.14 MAC Interface                                    |      |

| 2.15 OTG Interface                                    |      |

| 2.16 USB Port                                         |      |

| 2.17 RTC Interface                                    |      |

| 2.18 Clock Configuration Signal                       |      |

| 2.19 Power Ground                                     |      |

| 2.20 Initialization Signal                            |      |

| 3 Register Definition                                 | . 20 |

| 3.1 Base Register Definition                          | 20   |

| 3.2 Each Module Register Definition                   | 21   |

| 4 Clock Structure                                     | . 26 |

| 4.1 Clock Architecture                                |      |

| 4.2 Clock Signal Description                          |      |

| 5 Chip Configuration and Control                      |      |

| 5.1 Address space allocation                          |      |

| 5.1 Address space anocation                           |      |

| 5.2 Chip Configuration Register (CONFREG)             |      |

| 5.2.1 FLL/SDRAW Frequency configuration register      |      |

| J.2.2 OF UTCAMERATION IEquency configuration register |      |

$\leq$

| 5.2.3 SDRAM parameter register                                            | 29   |

|---------------------------------------------------------------------------|------|

| 5.2.4 SHUT CTRL register                                                  |      |

| 5.2.5 MISC_CTRL register                                                  | 31   |

| 5.2.6 cpu_throt register                                                  |      |

| 5.2.7 UART multiplex configuration register                               | 32   |

| 5.2.8 GPIO0 Configuration Register (corresponding GPIO[31:0])             | 33   |

| 5.2.9 GPIO1 configuration register (corresponding GPIO[63:32])            | 33   |

| 5.2.10 GPIO2 configuration register (corresponding GPIO[95:64])           | 34   |

| 5.2.11 GPIO3 configuration register (corresponding GPIO[127:96])          | 34   |

| 5.2.12 PAD[31:0] pin multiplex relation configuration register            | 34   |

| 5.2.13 PAD[63:32] pin multiplex relation configuration register           |      |

| 5.2.14 PAD[95:64] pin multiplex relation configuration register           |      |

| 5.2.15 PAD[127:96] pin multiplex relation configuration register          | 36   |

| 5.3 Interrupt Configuration Register                                      |      |

| 6 SDRAM Controller                                                        | . 42 |

| 6.1 Overview                                                              | 42   |

| 6.2 Register Description                                                  | 42   |

| 6.3 Software Configuration Description                                    |      |

| 6. CONFIG_VALID                                                           |      |

| 7 SRAM Controller                                                         |      |

| 7.1 Overview                                                              |      |

| 7.2 Configuration Register.                                               |      |

| 8 Camera Interface                                                        |      |

| 8.1 Overview                                                              |      |

| 8.2 Interface protocol                                                    |      |

| 8.3 Register Description                                                  |      |

| 8.4 Configuration Operations                                              |      |

| 8.4.1 Access memory mode                                                  |      |

| 8.4.2 Configuration order                                                 |      |

| 9 I2S Controller                                                          |      |

| 9.1 Overview                                                              |      |

|                                                                           |      |

| <ul><li>9.2 Interface protocol.</li><li>9.3 Dedicated Register.</li></ul> |      |

| 9.4 Configuration Operations                                              |      |

|                                                                           |      |

| 10 Display Controller (DC)                                                |      |

| 10.1 Overview                                                             |      |

|                                                                           |      |

| 10.2.1 Frame buffer configuration register                                |      |

| 10.2.2 Frame buffer address register 0                                    |      |

| 10.2.3 Frame buffer address register 1                                    |      |

| 10.2.4 Frame buffer span register                                         |      |

| 10.2.5 Color dithering configuration register                             |      |

| 10.2.6 Color vibrance lookup table low-bit register                       |      |

| 10.2.7 Color dithering lookup table high-bit register                     |      |

| 10.2.8 Color dithering description                                        |      |

| 10.2.9 LCD panel configuration register                                   |      |

| 10.2.10 Horizontal display with register                                  |      |

| 10.2.12 Vertical display height register                                  |      |

| 10.2.13 Field synchronization configuration register                      |      |

| 10.2.13 Field synchronization configuration register                      |      |

| 10.2.15 Gamma correction catalog register                                 |      |

| 10.2.16 Gamma correction value register                                   |      |

| 10.2.17 Gamma correction instructions                                     |      |

| 11 MAC Controller                                                         |      |

|                                                                           |      |

| 11.1 DMA Register Description                                             |      |

$\leq$

| 11.1.1 Register0 (Bus Mode Register)                                   | 59 |

|------------------------------------------------------------------------|----|

| 11.1.2 Register2 (Receive Poll Demand Register)                        |    |

| 11.1.3 Register2 (Receive Poll Demand Register)                        | 60 |

| 11.1.4 Register3 (Receive Descriptor List Address Register)            | 60 |

| 11.1.5 Register4 (Transmit Descriptor List Address Register)           | 60 |

| 11.1.6 Register5 (Status Register)                                     | 60 |

| 11.1.7 Register0 (Bus Mode Register)                                   |    |

| 11.1.8 Register7 (Interrupt Enable Register)                           |    |

| 11.1.9 Register8 (Missed Frame and Buffer Overflow Counter Register)   |    |

| 11.1.10 Register9(Receive Interrupt Watchdog Timer Register)           |    |

| 11.1.1 Register0 (Bus Mode Register)                                   |    |

| 11.1.12 Register11 (AXI Status Register)                               |    |

| 11.1.13 Register18 (Current Host Transmit Descriptor Register)         |    |

| 11.1.14 Register19 (Current Host Receive Descriptor Register)          |    |

| 11.1.15 Register20 (Current Host Transmit Buffer Address Register)     |    |

| 11.1.16 Register21 (Current Host Receive Buffer Address Register)      |    |

| 11.2 MAC Controller Register Description                               |    |

| 11.2.1 Register0 (MAC Configuration Register)                          |    |

| 11.2.2 Register1 (MAC Frame Filter)                                    |    |

| 11.2.3 Register2 (Hash Table High Register)                            |    |

| 11.2.4 Register3 (Hash Table Low Register)                             |    |

| 11.2.5 Register4 (GMII Address Register)                               |    |

| 11.2.6 Register5 (GMII Data Register)                                  |    |

| 11.2.7 Register6 (Flow Control Register)                               |    |

| 11.2.9 Registero (Flow Control Register)                               |    |

| 11.2.9 Register? (VErit Register)                                      |    |

| 11.2.10 Register14 (Interrupt Status Register)                         |    |

| 11.2.11 Register15 (Interrupt Mask Register)                           |    |

| 11.2.12 Register16 (MAC Address0 High Register)                        |    |

| 11.2.13 Register17 (MAC Address0 Low Register)                         |    |

| 11.2.14 Register18 (MAC Address1 High Register)                        |    |

| 11.2.15 Register19 (MAC Address1 Low Register)                         |    |

| 11.2.16 Register 48 (AN Control Register)                              |    |

| 11.2.17 Register49 (AN Status Register)                                |    |

| 11.2.17 Register50 (Auto-Negotiation Advertisement Register)           |    |

| 11.2.19 Register51 (Auto-Negotiation Link Partner Ability Register)    |    |

| 11.2.20 Register52 (Auto-Negotiation Expansion Register)               |    |

| 11.2.21 Register54 (SGMII/RGMII Status Register)                       |    |

| 11.2.22 Register448 (Time Stamp Control Register)                      |    |

| 11.2.23 Register449 (Sub-Second Increment Register)                    |    |

| 11.2.24 Register 450 (System Time - Seconds Register)                  |    |

| 11.2.25 Register 451 (System Time - Nanoseconds Register)              |    |

| 11.2.26 Register 452 (System Time - Seconds Update Register)           |    |

| 11.2.27 Register 453 (System Time - Nanoseconds Update Register)       |    |

| 11.2.28 Register 454 (Time Stamp Addend Register)                      |    |

| 11.2.29 Register 455 (Target Time Seconds Register)                    |    |

| 11.2.30 Register 456 (Target Time Nanoseconds Register)                |    |

| 11.2.31 Register 457 (System Time - Higher Word Seconds Register)      |    |

| 11.2.32 Register 458 (Time Stamp Status Register)                      |    |

| 11.2.32 Register 459 (PPS Control Register)                            |    |

| 11.2.34 Register 460 (PPS Auxiliary Time Stamp - Nanoseconds Register) |    |

| 11.2.35 Register 461 (PPS Auxiliary Time Stamp - Seconds Register)     |    |

| 11.3 DMA Descriptor                                                    |    |

| 11.3.1 Basic Format of DMA Descriptor                                  |    |

| 11.3.2 DMA receive descriptor                                          |    |

| 11.3.2.1 RDES0                                                         |    |

| 11.3.2.2 RDES1                                                         |    |

|                                                                        |    |

y

| 11.3.2.3 RDES2                                                   | 81   |

|------------------------------------------------------------------|------|

| 11.3.2.4 RDES3                                                   | 81   |

| 11.3.3 DMA transmit descriptor                                   | 81   |

| 11.3.3.1TDES0                                                    |      |

| 11.3.3.2TDES1                                                    |      |

| 11.3.3 3TDES2                                                    |      |

| 11.3.3.4TDES3                                                    |      |

| 11.4 Software Programming Guide                                  |      |

| 11.5 IEEE 1588 Support                                           |      |

| 12 USB Controller                                                |      |

|                                                                  |      |

| 12.1 Overview                                                    |      |

| 12.2 USB Host Controller Register                                |      |

| 12.2.1 EHCI relevant registers                                   |      |

| 12.2.2 Capability register                                       |      |

| 12.2.3 Operational Register                                      |      |

| 12.2.4 EHCI implementation relevant register                     |      |

| 12.3 OHCI Relevant Register                                      |      |

| 12.3.1 Operational Register                                      | 90   |

| 12.3.2 OHCI implementation relevant register                     |      |

| 13 OTG Controller                                                |      |

| 13.1 Overview                                                    |      |

| 13.2 Register Description                                        | 92   |

| 13.2.1 Global Control and Status Registers (Global CSR Map)      | 93   |

| 13.2.2 Host Mode Control and Status Register (Host Mode CSR)     |      |

| 13.2.3 Device Mode Control and Status Register (Device Mode CSR) | 94   |

| 13.2.4 Data FIFO Access Register MAP (DFIFO Access Register MAP) | 94   |

| 13.2.5 Power and Clock Gating CSR Map                            | 95   |

| 13.3 Register Description                                        | 95   |

| 13.3.1 Register access characteristics                           |      |

| 13.3.2 Global register                                           | 96   |

| 13.3.3 Host mode register                                        | .115 |

| 13.3.4 Device Mode Register                                      |      |

| 13.3.5 Power consumption and clock gating register               |      |

| 14 Common Use with DMA                                           |      |

| 14.1 DMA Controller Structural Description.                      |      |

| 14.2 DMA Register                                                |      |

| 14.2.1 ORDER ADDR IN                                             |      |

| 14.2.2 DMA ORDER ADDR                                            |      |

| 14.2.3 DMA_SADDR                                                 |      |

| 14.2.4 DMA_DADDR                                                 |      |

| 14.2.5 DMA_LENGTH                                                |      |

| 14.2.6 DMA_STEP_LENGTH                                           |      |

| 14.2.7 DMA_STEP_TIMES                                            |      |

| 14.2.9 DMA_STEL_TIMES<br>14.2.8 DMA_CMD                          |      |

| 14.3 Multiple Modules Use DMA Configuration Description          |      |

| 15 SPIO Controller                                               |      |

|                                                                  |      |

| 15.1 SPI Controller Structure                                    |      |

| 15.2 Configuration Register.                                     |      |

| 15.2.1 Control register (SPCR)                                   |      |

| 15.2.2 Status register (SPSR)                                    |      |

| 15.2.3 Data register (TxFIFO/RxFIFO)                             |      |

| 15.2.4 External register (SPER)                                  |      |

| 15.2.5 Parameter control register (SFC_PARAM)                    |      |

| 15.2.6 Chip selection control register (SFC_SOFTCS)              |      |

| 15.2.7 Timing sequence control register (SFC_TIMING)             |      |

| 15.3 Interface Time Sequence                                     |      |

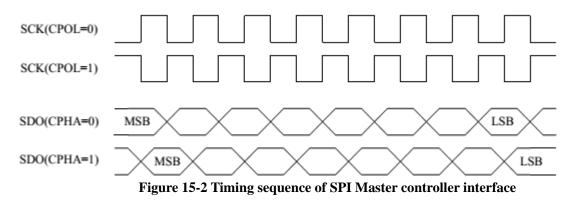

| 15.3.1 Timing sequence of SPI Master controller interface        | .145 |

V

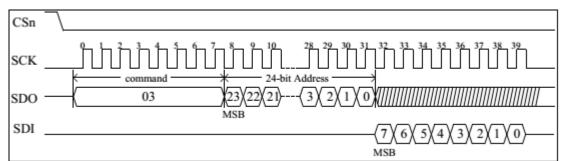

| 15.3.2 SPI Flash access timing sequence                                                         |       |

|-------------------------------------------------------------------------------------------------|-------|

| 15.4 User's Manual                                                                              |       |

| 15.4.1 Read and write operations of SPI master controller                                       |       |

| 15.4.2 Hardware SPI flash head                                                                  |       |

| 15.4.3 Mixed access to SPI Flash and SPI master controller                                      | 147   |

| 16 SPI1 Controller                                                                              | . 148 |

| 16.1 SPI Master Controller Structure                                                            | 148   |

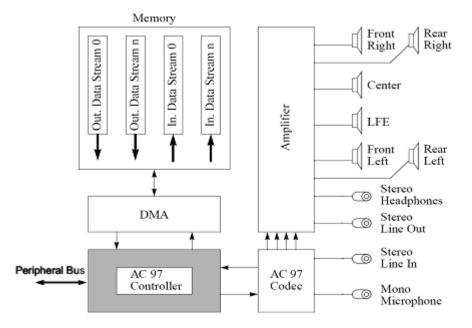

| 17 AC97 Controller                                                                              |       |

| 17.1 Overview (1C2 without the module)                                                          |       |

| 17.1 Overview (1C2 without the module)                                                          |       |

| 17.2 AC77 Controller Register                                                                   |       |

| 17.2.2 OCC register                                                                             |       |

| 17.2.3 ICC register                                                                             |       |

| 17.2.4 Codec register access command                                                            |       |

| 17.2.5 Interrupt status register/interrupt mask register                                        |       |

| 17.2.6 Interrupt status / clear register                                                        | 152   |

| 17.2.7 OC Interrupt clear register                                                              |       |

| 17.2.8 IC Interrupt clear register                                                              |       |

| 17.2.9 CODEC WRITE interrupt clear register                                                     |       |

| 17.2.10 CODEC READ interrupt clear register                                                     |       |

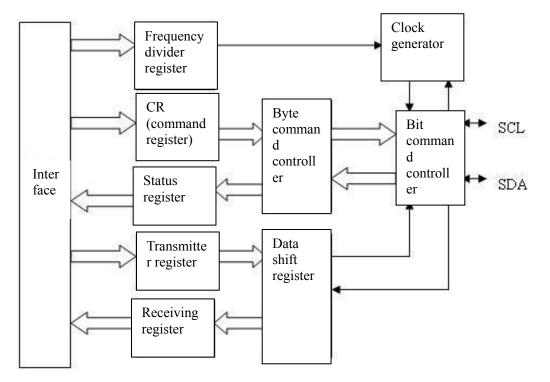

| 18 I2C Controller                                                                               |       |

|                                                                                                 |       |

| 18.1 Overview                                                                                   |       |

| 18.2 I2C Controller Structure                                                                   |       |

| 18.3 I2C Controller Register Description                                                        |       |

| 18.3.1 Frequency division latch low-byte register (PRERIo)                                      |       |

| 18.3.2 Frequency division latch high-byte register (PRERhi)                                     |       |

| 18.3.3 Control register (CTR)<br>18.3.4 Transmit data register (TXR)                            |       |

| 18.3.5 Receive data register (RXR)                                                              |       |

| 18.3.6 Command control register (CR)                                                            |       |

| 18.3.7 Status register (SR)                                                                     |       |

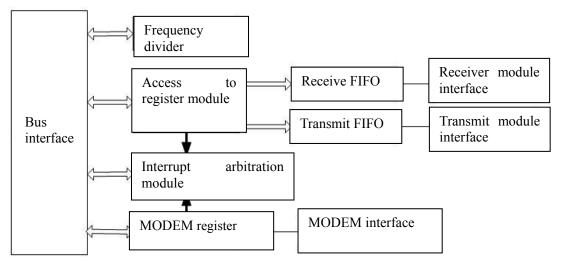

| 19 UART Controller                                                                              |       |

|                                                                                                 |       |

| 19.1 Overview                                                                                   |       |

| <ul><li>19.2 Controller Structure</li><li>19.3 UART0 Split Configuration Introduction</li></ul> |       |

| 19.3 OARTO Spin Computation Infoduction                                                         |       |

|                                                                                                 |       |

| 19.4.1 Data register (DAT)<br>19.4.2 Interrupt enable register (IER)                            |       |

|                                                                                                 |       |

| 19.4.3 Interrupt identification register (IIR)<br>19.4.4 FIFO control register (FCR)            | 139   |

| 19.4.5 Line control register (LCR)                                                              | 100   |

| 19.4.6 MODEM control register (MCR)                                                             | 161   |

| 19.4.7 Line status register (LSR)                                                               | 161   |

| 19.4.8 MODEM status register (MSR)                                                              |       |

| 19.4.9 Fractional frequency latch                                                               |       |

| 19.5 USART Register Description                                                                 |       |

| 19.5.1 Control register (CR)                                                                    |       |

| 19.5.2 Mode register (MR)                                                                       |       |

| 19.5.2 FI/DI parameter register (FIDIR)                                                         | 163   |

| 20 NAND Controller                                                                              |       |

| 20 NAND Controller Structural Description                                                       |       |

| 20.1 NAND Control Structural Description                                                        |       |

| 20.2 NAND Control Register Configuration Description                                            |       |

| 20.2.2 Page offset address register (ADDR_C)                                                    |       |

| 20.2.3 Page address register (ADDR_C)                                                           |       |

| 20.2.5 Tage address register (ADDR_R)                                                           |       |

|                                                                                                 |       |

$\leq$

| 20.2.5 ID register (ID_L)                                                                | 166   |

|------------------------------------------------------------------------------------------|-------|

| 20.2.6 ID and status register (STATUS & ID_H)                                            | 166   |

| 20.2.7 Parameter configuration register (NAND_PARAMETER)                                 | 166   |

| 20.2.8 Operating number register (NAND_OP_NUM)                                           | 167   |

| 20.2.9 Map register (CS_RDY_MAP)                                                         | 167   |

| 20.2.10 DMA read and write data register (DMA_ADDRESS)                                   | 167   |

| 20.3 NAND ADDR Description                                                               |       |

| 20.4 Examples of Nand-flash Read and Write Operations                                    | 170   |

| 20.5 NAND ECC Description                                                                |       |

| 20.6 NAND BOOT description                                                               |       |

| 21 RTC                                                                                   |       |

| 21.1 Overview                                                                            |       |

| 21.2 Register Description                                                                |       |

| 21.2.1 Register address list                                                             |       |

| 21.2.1 Register address list                                                             |       |

| 21.2.3 SYS_TOYWRITE1                                                                     | 173   |

| 21.2.5 STS_TOTWRITET                                                                     |       |

| 21.2.5 SYS TOYREAD1                                                                      |       |

| 21.2.5 SYS_TOYMATCH0/1/2 (no register in 1C2)                                            |       |

|                                                                                          |       |

| 21.2.7 SYS_RTCCTRL (no register in 1C2)<br>21.2.8 SYS_TOYMATCH0/1/2 (no register in 1C2) | 174   |

|                                                                                          |       |

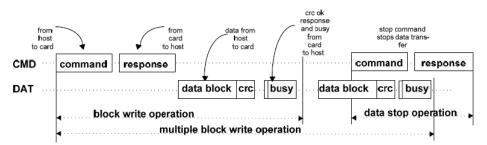

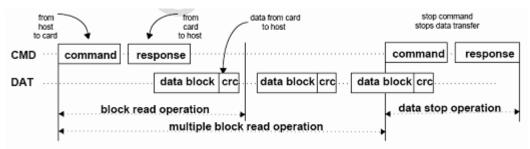

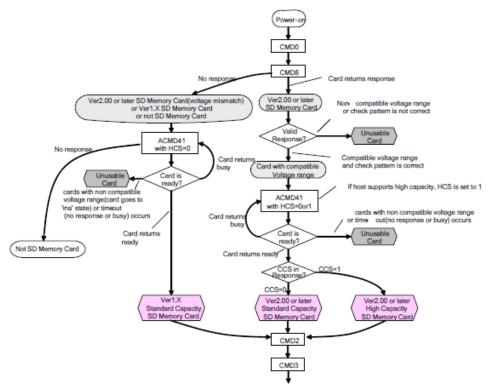

| 22 SDIO Controller                                                                       |       |

| 22.1 Function Overview                                                                   |       |

| 22.2 SDIO Protocol Overview                                                              |       |

| 22.3 Register Description                                                                | 177   |

| 22.4 Software Programming Instructions                                                   |       |

| 22.4.1 SD Memory card software programming instructions                                  |       |

| 22.4.2 SDIO card software programming instructions                                       |       |

| 23 CAN Controller 1                                                                      | 86    |

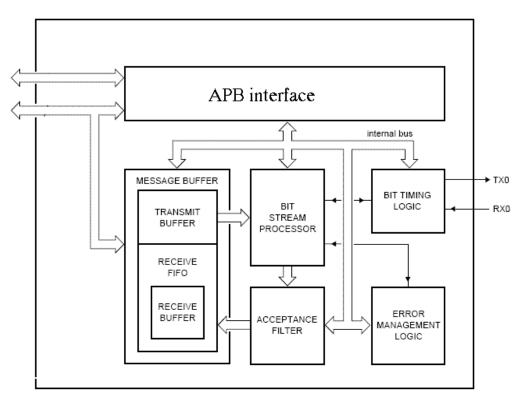

| 23.1 Overview                                                                            |       |

| 23.2 CAN Controller Structure                                                            | 186   |

| 23.3 Standard Mode                                                                       |       |

| 23.3.1 Standard mode address list                                                        | 187   |

| 23.3.2 Control register (CTR)                                                            | 188   |

| 23.3.3 Command register (CMR)                                                            | 188   |

| 23.3.4 Status register (SR)                                                              | 188   |

| 23.3.5 Interrupt register (IR)                                                           | 189   |

| 23.3.6 Acceptance Code Register (ACR)                                                    |       |

| 23.3.7 Acceptance Mask Register (AMR)                                                    |       |

| 23.3.8 Transmit buffer list                                                              |       |

| 23.3.9 Receive buffer list                                                               |       |

| 23.4 Extension Mode                                                                      |       |

| 23.4.1 Extension mode address table                                                      | 190   |

| 23.4.2 Mode register (MOD)                                                               |       |

| 23.4.3 Command register (CMR)                                                            |       |

| 23.4.4 Status register (SR)                                                              |       |

| 23.4.5 Interrupt register (IR)                                                           |       |

| 23.4.6 Interrupt enable register (IER)                                                   |       |

| 23.4.7 Arbitration Loss Capture Register (IER)                                           |       |

| 23.4.8 Error Alarm Limit Register (EMLR)                                                 |       |

| 23.4.9 RX Error Count Register (RXERR)                                                   |       |

| 23.4.10 TX Error Count Register (TXERR)                                                  |       |

| 23.4.11 Acceptance filter                                                                |       |

| 23.4.12 RX message count register (RMCR)                                                 |       |

| 23.5 Public Register                                                                     |       |

| 23.5.1 Bus timing register 0 (BTR0)                                                      |       |

| 23.5.2 Bus timing register 1 (BTR1)                                                      |       |

|                                                                                          | - / ! |

y

| 23.5.3 Output Control Register (OCR)     | 195 |

|------------------------------------------|-----|

| 24 ADC Controller                        |     |

| 24.1 Overview                            | 196 |

| 24.2 Register Description                |     |

| 24.3 Configuration Operations            |     |

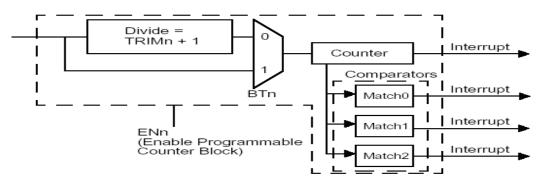

| 25 PWM Controller                        |     |

| 25.1 Overview                            |     |

| 25.2 PWM Register description            |     |

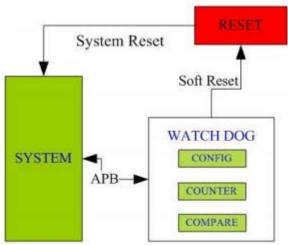

| 26 Watchdog (WDT)                        |     |

| 26.1 Overview                            |     |

| 26.2 Description of WATCHDOG Register    |     |

| 26.2.1 Watchdog Enable Register (WDT_EN) |     |

| 26.2.2 Watchdog Set Register (WDT_SET)   |     |

| 26.2.3 Watchdog Timer (WDT_timer)        |     |

| 27 High-precision Timer (HCNTR)          |     |

| 27.1 Overview                            |     |

| 27.2 Register Description                |     |

V

# List of Figures

| Figure 1-1 Architecture chart of Loongson 1C                                        | 10    |

|-------------------------------------------------------------------------------------|-------|

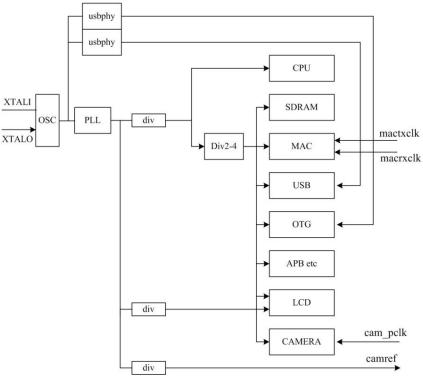

| Figure 4-1 System clock architecture                                                | 26    |

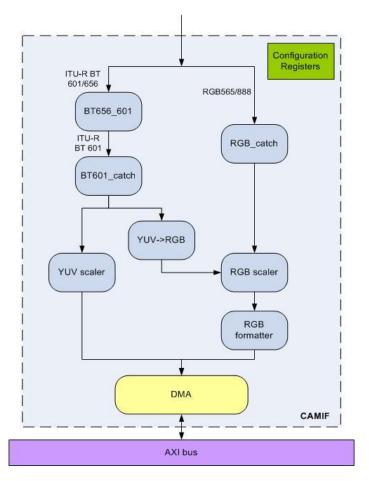

| Figure 8-1 Camera interface (CAMIF) functional diagram                              | 46    |

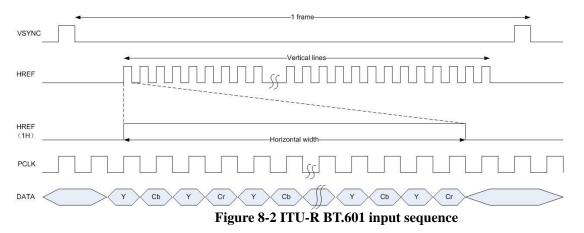

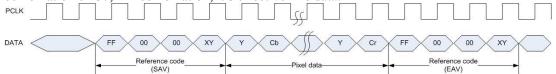

| Figure 8-2 ITU-R BT.601 input sequence                                              | 46    |

| Figure 8-3 ITU-R BT.656 input sequence                                              |       |

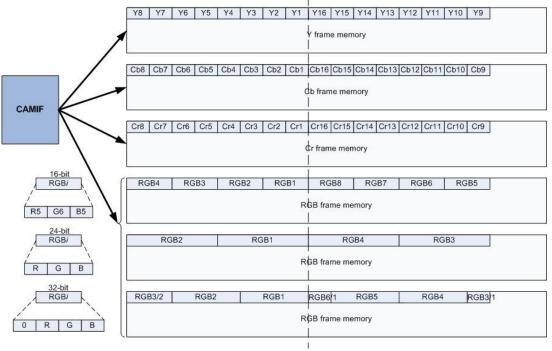

| Figure 8-4 Storage mode                                                             | 50    |

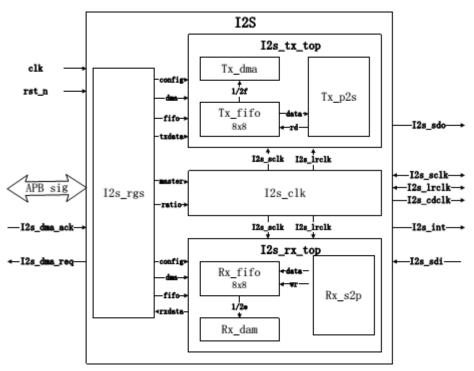

| Figure 9-1 I2S interface block diagram                                              | 51    |

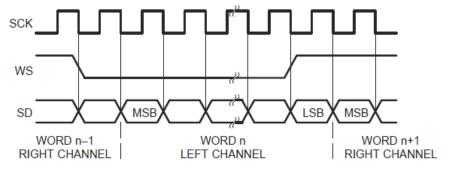

| Figure 9-2 I2S transmission protocol.                                               | 52    |

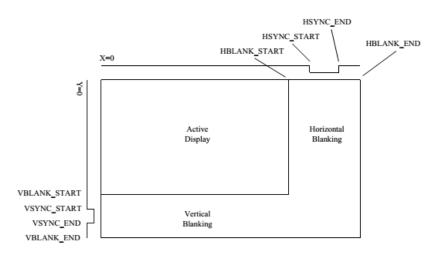

| Figure 10-1 Display controller output sequencing                                    | 57    |

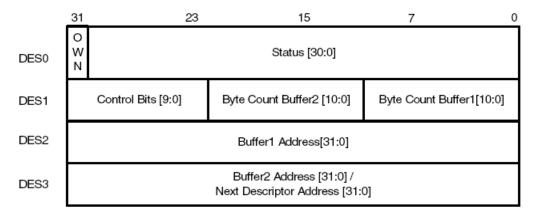

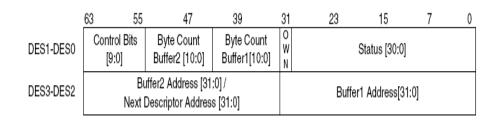

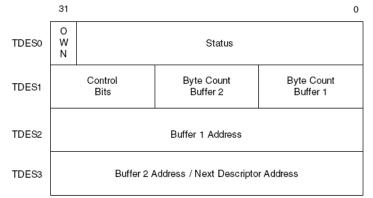

| Figure 11-1 Basic format of DMA descriptor (little end 32bit bus)                   |       |

| Figure 11-2 Basic format of DMA descriptor (little end 32bit bus)                   | 78    |

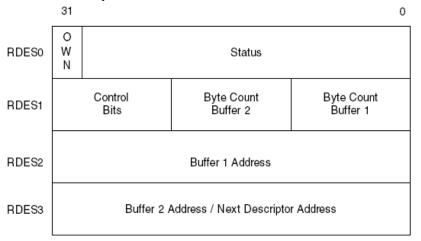

| Figure 11-3 Basic format of DMA receive descriptor (small end 32bit bus)            | 79    |

| Figure 11-4 Basic format of DMA transmit descriptor (little tailing end 32-bit bus) | 81    |

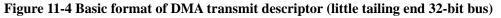

| Figure 11-5 Period clock synchronization process                                    | 85    |

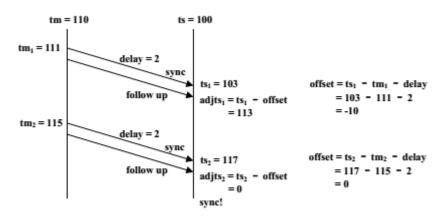

| Figure 11-6 Slave proactive synchronization process                                 | 85    |

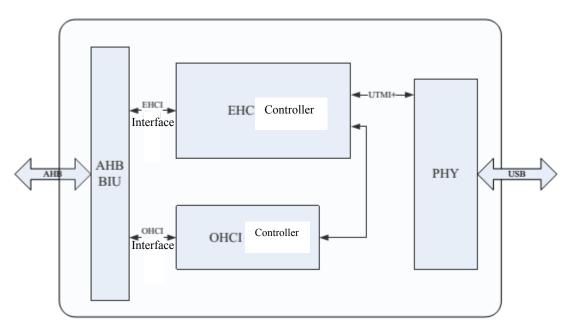

| Figure 12-1 USB host controller module                                              | 87    |

| Figure 13-1 OTG CSRs address mapping                                                |       |

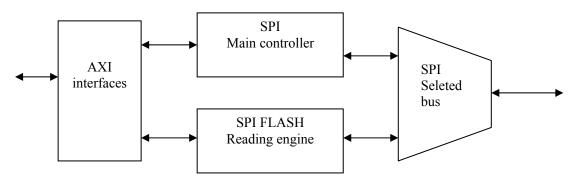

| Figure 15-1 SPI controller architecture                                             | . 143 |

| Figure 15-2 Timing sequence of SPI Master controller interface                      | . 145 |

| Figure 15-3 SPI Flash standard read timing sequence                                 | . 146 |

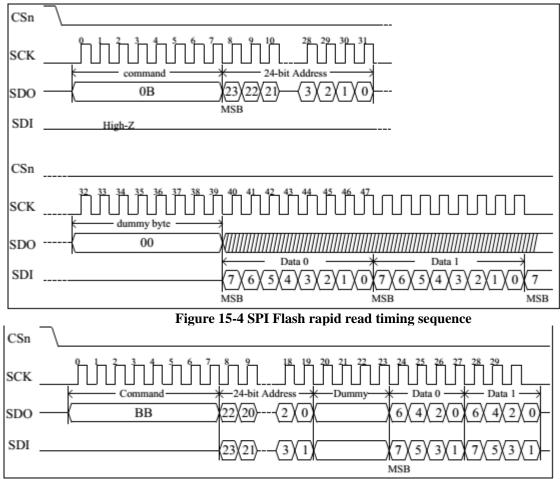

| Figure 15-4 SPI Flash rapid read timing sequence                                    | . 146 |

| Figure 15-5 SPI Flash directional I/O read timing sequence                          | . 146 |

| Figure 18-1 I2C Master Controller architecture                                      | . 154 |

| Figure 19-1 UART controller architecture                                            | . 157 |

| Figure 21-1 RTC block architecture diagram                                          | . 172 |

| Figure 22-1 Schematic diagram of SD card multi-block write operation                | . 176 |

| Figure 22-2 Schematic diagram of SD card multi-block read operation                 | . 176 |

| Figure 22-3 Schematic diagram of SD Memory card initialization process              | . 184 |

| Figure 23-1 CAN master controller architecture                                      | . 186 |

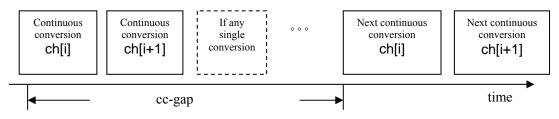

| Figure 24-1 Schematic diagram of ADC single conversion/continuous conversion        | . 201 |

| Figure 26-1 Watchdog architecture chart                                             | . 205 |

$\leq$

# List of Tables

| Table 2-1 Signal Type Code                                       | 14  |

|------------------------------------------------------------------|-----|

| Table 4-1 Loongson 1C clock signal                               |     |

| Table 8-1 ITU-R BT.656 reference code                            |     |

| Table 8-2 The fourth byte XY value                               |     |

| Table 15-1 SPI frequency division factor                         | 144 |

| Table 19-1 Configuration and function multiplexing of UART split |     |

| Table 20-1 NAND address space diagram                            |     |

| Table 22-1 Command format in SD mode                             |     |

# **1 Overview**

Loongson 1C chip is a cost-effective single chip system based on LS232 processor core, and is applicable to fields such as biological recognition of fingerprints and Internet of Things sensing.

1C includes the floating point processing unit, and can effectively enhance the processing ability of system floating point data. The memory interface of 1C supports several types of memories and allows the flexible system design. It supports 8-bit SLC NAND or MLC NAND FLASH, and provides the storage expansion interface of high capacity.

1C has provided various serial peripheral interfaces and on-chip modules for developers, including Camera controller, USB OTG 2.0 and USB HOST 2.0 interfaces, AC97/I2S controller, LCD controller, ADC controller, high-speed SPI interface, full-function UART interface, and owns the sufficient computing ability and multi-application connecting ability. It integrates RTC function, and is used to maintain the real time clock.

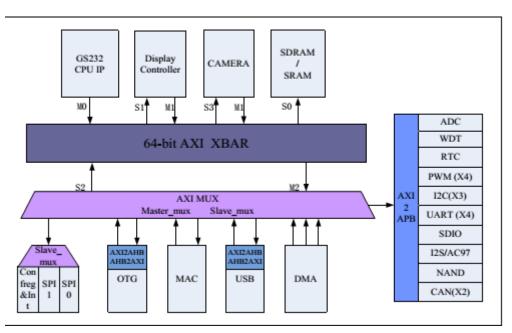

#### **1.1 System Architecture Chart**

Hierarchical bus architecture is adopted inside Loongson 1C. Processor core, memory controller, graphic display controller, CAMERA interface module and AXI\_MUX are interconnected by crossbar OTG, MAC, USB and DMA controllers and SPI are connected to crossbar via AXI\_MUX. Low-speed peripherals (I2C, I2S, PWM, UART, etc.) are connected to crossbar via AXI2APB.

Figure 1-1 Architecture chart of Loongson 1C

### **1.2 Main Functions of the Chip**

#### 1.2.1 Processor core

- Instruction sets of single core LS232 and MIPS32 are compatible, and the dominant frequency is 300MHZ.

- It supports the highly effective dual-issue technology (one clock tick performs two instructions)

- It supports the out-of-order issue and execution technologies such as register renaming, dynamic scheduling, and branch prediction

- 5-stage pipeline(instruction fetch, coding, issue, execution, write back and submit ) microarchitecture

- 16KB data cache and 16KB instruction cache

- It integrates 64bit floating point processing unit, supports the fully pipelining of 64bit floating point additive and multiplying operation. Its hardware has accomplished the floating point division operation.

#### **1.2.2 SDRAM Controller**

- SDRAM operation, operating frequency of 45~133MHz

- It supports the bus width of 8/16bit parallel data.

- It supports the auto-refresh and self-refresh functions, and page mode.

#### 1.2.3 SRAM/NOR FLASH Controller

- SRAM and NOR Flash direct link interface, working frequency of 66~133MHz

- It supports the chip select pin of static memory, and can be configured separately.

- It supports the bus width of 8bit/16bit parallel data.

#### **1.2.4 NAND Controller**

- It supports the single capacity of 4GB NAND FLASH at most

- It supports the FLASH of 512 bytes, 2K byte page, 4K byte page and 8K byte page.

- Hardware ECC generation, detection and indication (software error correction)

- It supports the data reading speed of 8~10MB/S and writing speed of 5MB/s from Flash

- It supports the boot from NAND Flash

- Support mode of little endian

#### 1.2.5 Clock generator

- It has one standard PLL input interface, and supports the external crystal as chip clock input.

- It supports the on-chip output and can configure one way of clock for off-chip peripherals.

- PLL configurable frequency software

#### **1.2.6 I<sup>2</sup>S controller**

- It supports I<sup>2</sup>S input in master mode

- It supports  $I^2S$  output in master mode

- It supports the width of 8, 16, 18, 20, 24 and 32 bits.

- It supports audio data of mono and stereo

- It supports the sampling frequency of (16, 22.05, 32, 44.1 and 48) kHz

- It supports DMA transmission mode

#### 1.2.7 AC97 controller

- Variable sampling rate AC97 coder and decoder interfaces (48KHz and below)

- It supports the stereo PCM and single-track MIC input

- It supports 2-channel stereo PCM output

- It support DMA and interrupt operation

- It supports 16, 18 and 20bits sampling precision, and variable sampling rate.

- It supports 16bits, and 16 entry FIFOs for each channel.

#### 1.2.8 LCD controller

- It support 16/24-bit pixel mode

- It supports the display output of RGB444/555/565/888

- It supports the pixel of 1024x768, 800x600, 640-x480 and 320-x240

- It supports DMA transmission mode

#### **1.2.9** Camera interface

- It supports ITU-R BT.601/656 8bit input.

- It supports RAW RGB, RGB565 and YUV4:2:2 data input.

- It supports YUV, RGB888, RGB0888 and RGB565 outputs

- It supports the pixel zooming of 320x240 and 640x480

- It supports the pixel input of 2Kx2K at most, and the pixel can be configured.

- It supports DMA transmission mode

#### 1.2.10 MAC controller

- It supports 10/100Mbps PHY device, including 10 Base-T, 100 Base-TX, 100Base-FX and 100 Base-T4;

- It's completely compatible with IEEE standard 802.3

- It's completely compatible with 802.3x full duplex flow control and half-duplex back pressure flow control

- It supports VLAN frames

- It supports DMA transmission mode

- It supports standard media independent interface (MII)

- It supports the standard simplified MII interface (RMII), and may connect the external PHY chip.

#### 1.2.11 USB2.0 controller

- One USB OTG2.0 controller

- One USB HOST2.0 controller

- It supports high-speed and full-speed mode

- It supports DMA transmission mode

- It's compatible with USB Rev 1.1 and USB Rev 2.0 protocols

#### 1.2.12 SPI controller

- It supports two-way independent SPI interface, and each way of SPI interface supports four chip selects.

- Follow specifications of serial peripheral interface (SPI)

- It supports synchronous, serial and full duplex communication

- It supports SPI master mode

- 8-bit in per transmission

- It supports inquiries and interrupt transmission mode

- It supports the SPI nor flash boot.

- It supports SPI interface two-way input and output, and the maximum data transmission speed is 24~96 Mbps.

- It supports the minimum communication rate as low as 25KB, and facilitates the matching of special device.

#### **1.2.13 I<sup>2</sup>C controller**

- Three-channel standard  $I^2C$  bus interface

- It supports configuration of master, slave or master / slave mode

- Programmable bus clock frequency

#### 1.2.14 UART controller

- It supports two full-function serial ports. Therein, the full-function serial port 0 can multiplex four two-wire serial interfaces or two four-wire serial interfaces, and supports the smart card protocol.

- RxD0, TxD0, RxD1, TxD1, RxD2 and TxD2 based on interrupt operation;

- UART channel 0, 1 and 2 with IrDA 1.0

- UART channel 0 and 1 with RTS0, CTS0, RTS1 and CTS1

#### 1.2.15 GPIO

- It supports 105 GPIO at most

- All GPIO (except boot and system configuration) is defaulted as input after reset

- All GPIO support interrupt function

- Each GPIO pin supports the level-triggered and edge-triggered modes, and can be configured independently.

- GPIO base pin rate up to 4MHz

#### 1.2.16 PWM controller

- Four-way 32bits can configure PWM timer.

- It supports timer function

- It supports counter function

#### 1.2.17 RTC

- Timing is accurate to 0.1 second

- It supports the external crystal as RTC clock input.

- It supports the operation powered by external battery, and later by battery after powered off.

- The special power pin may be connected to the battery or 3.3V main power supply.

- Provide seconds, minutes, hours, days, months and years

#### 1.2.18 CAN controller

2-channel independent CAN controller

- It's compatible with CAN2.0A and CAN2.0B protocols (the passive expansion frame in PCA82C200 compatible mode)

- It supports CAN protocol extensions

- Bit rate up to 1Mbits / s

#### **1.2.19 SDIO controller**

- channel independent CAN controller

- It's compatible with SD Memory 2.0/MMC/SDIO 2.0 protocol.

- It supports SDIO start

#### **1.2.20 ADC controller**

- Sampling rate up to 1MHz at most

- 4-channel ADC input

- It supports 4-wire and 5-wire touch screens

- It supports continuous sampling and single sampling

- It supports analog watchdog

# **2** Definition of Pin

#### **2.1 Conventions**

The instructions of Loongson 1C pin in this chapter use the following protocols: The input and output types of signals are represented by code. See Table 2-1.

| Table 2-1 Signal Type Code |                    |  |  |

|----------------------------|--------------------|--|--|

| Code                       | Description        |  |  |

| А                          | Simulation         |  |  |

| DIFF I/O                   | Two-way difference |  |  |

| DIFF IN                    | Difference input   |  |  |

| DIFF OUT                   | Difference output  |  |  |

| Ι                          | Input.             |  |  |

| I/O                        | Bidirectional      |  |  |

| 0                          | Output             |  |  |

| OD                         | Open-drain output  |  |  |

| Р                          | Power supply       |  |  |

| G                          | Ground             |  |  |

#### **2.2 LCD Interface**

| Signal name   | Туре | Pull-up/pull-<br>down | Description                       |

|---------------|------|-----------------------|-----------------------------------|

| LCD CLK       | 0    | PU                    | LCD clock signal                  |

| LCD_HSYNC     | 0    | PU                    | LCD horizontal synchronizing      |

|               |      |                       | signal                            |

| LCD_VSYNC     | 0    | PU                    | LCD vertical synchronizing signal |

| LCD_EN        | 0    | PU                    | LCD enable signal                 |

| LCD_DAT[15:0] | 0    | PU                    | LCD data signal                   |

[Notes] In QFP100 package, LCD interface can't be used. In QFP176 encapsulation, LCD may use 16bit and 24bit mode. In 16bit mode, the pin won't be multiplexed; in 24bit mode, the low bit needs to multiplex CAM DAT [7:0] or MAC signal.

#### **2.3 SDRAM Interface**

| Signal name   | Туре | Pull-up/<br>pull-down | Description                                   |

|---------------|------|-----------------------|-----------------------------------------------|

| SD_CLK        | Ο    | -                     | SDRAM clock signal                            |

| SD_CKE        | Ο    | -                     | SDRAM clock enable signal                     |

| SD_CSn        | Ο    | -                     | SDRAM chip selection signal, active low       |

| SD_RASn       | 0    | -                     | SDRAM line gating signal, effective low level |

| SD_CASn       | 0    | -                     | SDRAM column selection signal, active low     |

| SD_WE         | 0    | -                     | SDRAM read-write signal, writing as low level |

| SD_BA[1:0]    | 0    | -                     | Bank signal of SDRAM, four banks in total     |

| SD_ADDR[12:0] | 0    | -                     | SDRAM address signal                          |

| SD_DATA[15:0] | I/O  | -                     | SDRAM data signal                             |

| SD_DQM[1:0]   | 0    |                       | SDRAM data mask signal                        |

#### 2.4 SRAM/NOR Flash Interface

| Signal name     | Туре | Pull-up/<br>pull-down | Description                            |

|-----------------|------|-----------------------|----------------------------------------|

| SRAM_CSn        | 0    | -                     | SRAM chip selection signal, active low |

| SRAM_WEn        | 0    | -                     | SRAM writing enable signal, active low |

| SRAM_OEn        | 0    | -                     | SRAM reading enable signal, active low |

| SRAM_OEn        | 0    | -                     | SRAM reading enable signal, active low |

| SRAM_DATA[15:0] | I/O  | -                     | SRAM data signal                       |

| SRAM_BHE        | 0    |                       | SRAM high Byte Data desired signal     |

| SRAM_BLE        | 0    |                       | SRAM low Byte Data effective signal    |

#### **2.5 I2S Interface**

| Signal name | Туре | Pull-up/<br>pull-down | Description                   |

|-------------|------|-----------------------|-------------------------------|

| I2S_MCLK    | 0    | PU                    | I2S clock signal              |

| I2S_BCLK    | 0    | PU                    | I2S bit clock signal          |

| I2S_LRCK    | 0    | PU                    | I2S channel selection signal  |

| I2S_DI      | Ι    | PU                    | I2S data serial input signal  |

| I2S_DO      | 0    | PU                    | I2S data serial output signal |

[Notes] In QFP100 package, I2S interface isn't introduced, and needs to be multiplexed with MAC pin. In QFP176 package, I2S interface is introduced, and can be directly used.

#### 2.6 I 2C Interface

|   | Signal name            | Туре | Pull-up/       | Description                   |

|---|------------------------|------|----------------|-------------------------------|

|   |                        |      | pull-down      |                               |

|   | I2C[2:0]_SCL           | 0    | No elicitation | I <sup>2</sup> C serial clock |

|   | I2C[2:0]_SDA           | I/O  | No elicitation | I <sup>2</sup> C serial data  |

| Ļ | $\frac{12C[2.0]}{5DA}$ |      |                |                               |

[Notes] In QFP100 and QFP176 packages, I2C interface isn't introduced, and needs to be multiplexed with MAC, EJTAG, LCD or CAM pin.

#### **2.7 UART Interface**

| Signal name | Туре | Pull-up/<br>pull-down | Description                |

|-------------|------|-----------------------|----------------------------|

| UART0_TX    | 0    | PU                    | UART0 data transmission    |

| UART0_RX    | Ι    | PU                    | UART0 data reception       |

| UART0_RTS   | Ι    | PU                    | UART0 reception request    |

| UART0_CTS   | Ι    | PU                    | UART0 reception permission |

| UART0_DSR   | Ι    | PU                    | UART0 device ready         |

| UART0_DTR   | 0    | PU                    | UART0 data terminal ready  |

| UART0_DCD   | Ι    | PU                    | UART0 carrier detection    |

| UART0_RI    | Ι    | PU                    | UART0 ringing tips         |

[Notes] In QFP100 package, there is no full-function serial interface, and only two-wire type. In QFP176D

package, the full-function serial interface can be directly used.

#### **2.8 PWM Interface**

| Signal name | Туре | Pull-up/       | Description         |

|-------------|------|----------------|---------------------|

|             |      | pull-down      |                     |

| PWM0        | 0    | PU             | PWMO impulse output |

| PWM1        | 0    | PU             | PWM1 impulse output |

| PWM2        | 0    | No elicitation | PWM2 impulse output |

| PWM3        | 0    | No elicitation | PWM3 impulse output |

[Notes] In QFP100 package, PWM isn't introduced and needs to be multiplexed with others. In QFP176 package, PWM0 and PWM1 can be directly used, and PWM2 and PWM3 need to be multiplexed with others.

#### **2.9 ADC Interface**

| Signal name | Туре | Pull-up/<br>pull-down | Description                                   |

|-------------|------|-----------------------|-----------------------------------------------|

| ADC REXT    | Ι    | -                     | ADC reference resistor                        |

| ADC_VREF    | Ι    | -                     | ADC reference voltage                         |

| ADC_VDDA    | Ι    | -                     | ADC analog power supply                       |

| ADC_VSSA    | Ι    | -                     | ADC analog ground                             |

| ADC_D0      | Ι    | -                     | ADC Channel Zero sampling input               |

| ADC_D1      | Ι    | -                     | ADC Channel 1 sampling input                  |

| ADC_XP      | Ι    | -                     | The 2 <sup>nd</sup> channel sampling input of |

|             |      |                       | touch screen X+/ADC                           |

| ADC_YP      | Ι    | -                     | The 3rd channel sampling input of             |

|             |      |                       | touch screen X+/ADC                           |

[Notes] The AD interface can only be used In QFP176A package.

#### 2.10 SPI Interface

| Signal name  | Туре | Pull-up/<br>pull-down | Description               |

|--------------|------|-----------------------|---------------------------|

|              |      | puii-dowii            |                           |

| SPI_SCK      | 0    | PU                    | SPI clock output          |

| SPI[3:0]_CSn | 0    | PU                    | SPI chip selection 0 to 3 |

| SPI_MOSI     | 0    | PD                    | SPI data output           |

| SPI_MISO     | Ι    | PD                    | SPI data input            |

#### 2.11 EJTAG Interface

| Signal name | Туре | Pull-up/  | Description                        |

|-------------|------|-----------|------------------------------------|

|             |      | pull-down |                                    |

| EJTAG_SEL   | Ι    | PU        | JTAG selection(0: JTAG, 1: EJTAG)  |

|             |      |           | JTAG pin function multiplex (when  |

| JTAG_SEL    | Ι    | PU        | the bit is 1, select the multiplex |

|             |      |           | function)                          |

| EJTAG_TCK   | Ι    | PU        | JTAG clock                         |

| EJTAG_TDI   | Ι    | PU        | JTAG data input                    |

| EJTAG_TMS   | Ι    | PU        | JTAG mode                          |

| EJTAG_TRST  | Ι    | PU        | JTAG reset, to be pull down        |

| EJTAG TDO   | 0    | PU        | JTAG data output                   |

[Notes] EJTAG\_SEL select whether is JTAG or EJTAG JTAG\_SEL is used to choose JTAG multiplex function. Please don't be confused.

#### 2.12 CAMERA Interface

| Signal name  | Туре | Pull-up/<br>pull-down | Description                          |

|--------------|------|-----------------------|--------------------------------------|

| CAM_CLKOUT   | 0    | PU                    | Camera reference clock output        |

| CAM_PCLK_I   | Ι    | PU                    | Camera pixel clock input             |

| CAM_HSYNC    | Ι    | PU                    | Camera horizontal synchronization    |

|              |      |                       | signal                               |

| CAM_VSYNC    | Ι    | PU                    | Camera vertical synchronizing signal |

| CAMDATA[7:0] | Ι    | PU                    | Camera data input                    |

[Notes] In QFP100 packaging, CAM isn't bounded out and needs to be multiplexed with NAND and MAC. In QFP176 package, CAM can be directly used.

#### **2.13NAND Interface**

| Signal name  | Туре | Pull-up/<br>pull-down | Description               |

|--------------|------|-----------------------|---------------------------|

| NAND_CLE     | 0    | PD                    | NAND command latch        |

| NAND_ALE     | 0    | PD                    | NAND address latch        |

| NAND_RD      | 0    | PD                    | NAND read signal          |

| NAND_WR      | 0    | PD                    | NAND write signal         |

| NAND_CE      | 0    | PD                    | NAND chip selection 0     |

| NAND_RDY     | Ι    | PD                    | NAND ready 0              |

| NAND_D [7:0] | I/O  | PD                    | NAND address / data lines |

#### 2.14 MAC Interface

| Signal name  | Туре | Pull-up/<br>pull-down | Description                |

|--------------|------|-----------------------|----------------------------|

| MAC TXCK     | 0    | PU                    | MII clock transmission     |

| MAC_TXEN     | 0    | PU                    | MII control transmission   |

| MAC_TXD[3:0] | 0    | PU                    | MII data transmission      |

| MAC_RXCK     | Ι    | PU                    | MII clock reception        |

| MAC_RXDV     | Ι    | PU                    | MII control reception      |

| MAC_RXD[3:0] | Ι    | PU                    | MII data reception         |

| MAC_MDCK     | 0    | PU                    | SMA interface clock        |

| MAC_MDIO     | I/O  | PU                    | SMA interface data         |

| MAC_COL      | Ι    | PU                    | MAC Collision detection    |

| MAC_CRS      | Ι    | PU                    | MAC carrier wave detection |

[Notes] In QFP package, MAC can only use RMII mode. In QFP176 package, MII and RMII modes can be used.

#### 2.15 OTG Interface

| Signal name | Туре     | Pull-up/<br>pull-down | Description                      |

|-------------|----------|-----------------------|----------------------------------|

| OTG_DVDD    |          |                       | OTG digital power                |

| OTG_DVSS    |          |                       | OTG digital ground               |

| OTG_VDD33   |          |                       | OTG analog power supply          |

| OTG_VSS33   |          |                       | OTG analog ground                |

| OTG_REXT    |          |                       | OTG reference resistor           |

| OTG_DP      | DIFF I/O | -                     | OTG differential signal line D + |

| OTG_DM      | DIFF I/O | -                     | OTG differential signal line D – |

| OTG_VBUS    |          |                       | OTG_VBUS                         |

| OTG_ID      |          |                       | OTG_ID                           |

#### 2.16 USB Port

| Signal name | Туре     | Pull-up/<br>pull-down | Description                      |

|-------------|----------|-----------------------|----------------------------------|

| USB_DVDD    |          |                       | USB digital power                |

| USB_DVSS    |          |                       | USB digital ground               |

| USB_VDD33   |          |                       | USB analog power supply          |

| USB_VSS33   |          |                       | USB analog ground                |

| USB_REXT    |          |                       | USB reference resistor           |

| USB_DP      | DIFF I/O | -                     | USB differential signal line D + |

| USB_DM      | DIFF I/O | -                     | USB differential signal line D – |

[Notes] In QFP100 package, USB HOST can't be used. In QFP176 package, it can be used.

#### **2.17 RTC Interface**

| Signal name | Туре | Pull-up/pull- | Description                           |

|-------------|------|---------------|---------------------------------------|

|             |      | down          |                                       |

| RTC_CLK_I   | Ι    | -             | RTC oscillator input, connect 32.768K |

|             |      |               | oscillator                            |

| RTC_CLK_O   | 0    | -             | RTC crystal oscillator output         |

| VR_VDDA     |      |               | RTC power supply                      |

#### 2.18 Clock Configuration Signal

| Signal name | Туре | Pull-up/pull- | Description                                           |

|-------------|------|---------------|-------------------------------------------------------|

|             |      | down          |                                                       |

| XTALI       | I    |               | System clock crystal oscillator input, connect to 24M |

| XTAL0       | 0    | -             | System clock crystal oscillator output                |

#### 2.19 Power Ground

| Signal name | Туре | Pull-up/pull- | Description                   |

|-------------|------|---------------|-------------------------------|

|             |      | down          |                               |

| PLL_VDD33   | Р    |               | Core PLL analog power supply  |

| PLL_VSS33   | G    |               | Core PLL analog ground        |

| PLL_VDD12   | Р    |               | Core PLL digital power supply |

| PLL_VSS12   | G    |               | Core PLL digital ground       |

| CORE_VDD    | Р    |               | Core voltage power supply     |

| CORE_VSS    | G    |               | Core voltage ground           |

| IO_VDD      | Р    |               | IO power supply               |

#### 2.20 Initialization Signal

Loongson 1C has three starting modes: SPI FLASH, NAND FLASH and SDIO. Multiplex function pin obtains the configuration message from the pull-up and pull-down values during system reset for the software to judge the powered state.

| T 1 1 A 1 | 0 0           | • 1       |

|-----------|---------------|-----------|

| Table 2-1 | Configuration | signal    |

| 14010 2 1 | Comparation   | i bigiiai |

-18-

| Pin name     | Signal name | Description                                              |

|--------------|-------------|----------------------------------------------------------|

| NAND_D [3:0] | start_freq  | CPU PLL frequency configuration in hardware control mode |

|              |             | The frequency calculation formula shall be:              |

|              |               | $Freq = 6*(4*NAND_D[3:0] + 40)$                                                                                 |

|--------------|---------------|-----------------------------------------------------------------------------------------------------------------|

| NAND_D [5:4] | boot_sel      | Boot selection is different in QFP100 and QFP176 packages (in QFP100 packages, the control signal of NAND isn't |

|              |               | bonded to the pin)                                                                                              |

|              |               | In QFP100 package, boot sel is                                                                                  |

|              |               | 00: Reserved                                                                                                    |

|              |               | 01: it indicates the boot from SPI flash                                                                        |

|              |               | 10: it indicates the boot from NAND flash (multiplex                                                            |

|              |               | SDRAM pin)                                                                                                      |

|              |               | 11: it indicates the boot from NAND flash (multiplex MAC                                                        |

|              |               | pin)                                                                                                            |

|              |               | In QFP176 packaging, boot_sel is                                                                                |

|              |               | 00: Reserved                                                                                                    |

|              |               | 01: it indicates the boot from SPI flash                                                                        |

|              |               | 10: it indicates the boot from NAND flash                                                                       |

|              |               | 11: it indicates the boot from SDIO                                                                             |

| NAND_D [7:6] | nand_type     | In NAND boot, configure the capacity of NAND flash                                                              |

|              |               | 00: it indicates that the capacity is equal to 2Gb (2KB page)                                                   |

|              |               | 01: it indicates that capacity is 1Gb (2KB page)                                                                |

|              |               | 10: it indicates that the capacity is 512Mb (512 Bytes page)                                                    |

|              |               | 11: it indicates the capacity is low and equal to 256MB (512                                                    |

|              |               | Bytes page)                                                                                                     |

| NAND_CLE     | rs_rd_cfg     | In NAND boot, whether to adopt ECC, select NAND only in                                                         |

|              |               | boot_sel                                                                                                        |

|              |               | Flash valid at startup                                                                                          |

|              |               | When the bit is 0, it indicates the non-ECC boot of NAND                                                        |

|              |               | When the bit is 1, it indicates the ECC boot of NAND                                                            |

| SPI0_CLK     | usb_retclksel | Clock selective signal of USB_HOST and USB_OTG                                                                  |

|              |               | When the bit is 1, it indicates the clock is provided by PLL.                                                   |

|              |               | When the bit is 0, it indicates the clock is provided by                                                        |

|              |               | external oscillator.                                                                                            |

# **3 Register Definition**

### **3.1 Base Register Definition**

| Register name      | Address     | RW<br>(read/write)<br>(R/W) | Function description                                                  | Reset value |

|--------------------|-------------|-----------------------------|-----------------------------------------------------------------------|-------------|

| Base register      |             |                             |                                                                       |             |

| START_FREQ         | 0xbfe7_8030 | R/W                         | PLL frequency configuration<br>and SDRAM frequency<br>division factor |             |

| CLK_DIV_PARAM      | 0xbfe7_8034 | R/W                         | CPU/CAMERA/DC<br>frequency division factor                            | 0x0         |

| CBUS CONFSIGNALS   | 0xbfd0 0400 | R/W                         |                                                                       | 0x0         |

| CBUS_SD_CTRL0      | 0xbfd0_0410 | R/W                         | SDRAM parameter configuration register                                | 0x001438a3  |

| CBUS_SD_CTRL1      | 0xbfd0_0414 | R/W                         |                                                                       | 0x80000080  |

| SHUT CTRL          | 0xbfd0 0420 | R/W                         |                                                                       | 0x0         |

| MISC_CTRL          | 0xbfd0_0424 | R/W                         | Function multiplexing<br>register 0                                   |             |

| cpu throt          | 0xbfe7_c010 | R/W                         | CPU dynamic frequency reduction register                              | 0x0         |

| Interrupt register |             |                             |                                                                       |             |

| INTISR0            | 0xbfd0_0140 | R                           | Interrupt status register 0                                           | 0x0         |

| INTEN0             | 0xbfd0_0144 | R/W                         | Interrupt enable register 0                                           | 0x0         |

| INTSET0            | 0xbfd0_0148 | R/W                         | Interrupt setting register 0                                          | 0x0         |

| INTCLR0            | 0xbfd0_014c | R/W                         | Interrupt clear register 0                                            | 0x0         |

| INTPOL0            | 0xbfd0_0150 | R/W                         | Interrupt triggering level flag                                       | r           |

|                    |             |                             | register 0                                                            | 0x0         |

| INTEDGE0           | 0xbfd0_0154 | R/W                         | Interrupt triggering edge flag<br>register 0                          | ,<br>0x0    |

| INTISR1            | 0xbfd0 0158 | R                           | Interrupt status register 1                                           | 0x0         |

| INTEN1             | 0xbfd0_015c | R/W                         | Interrupt enable register 1                                           | 0x0         |

| INTSET1            | 0xbfd0 0160 | R/W                         | Interrupt setting register 1                                          | 0x0         |

| INTCLR1            | 0xbfd0_0164 | R/W                         | Interrupt clear register 1                                            | 0x0         |

| INTPOL1            | 0xbfd0 0168 | R/W                         | Interrupt triggering level flag<br>register 1                         | 0x0         |

| INTEDGE1           | 0xbfd0 016c | R/W                         | Interrupt triggering edge flag<br>register 1                          | 0x0         |

| INTISR2            | 0xbfd0 0170 | R                           | Interrupt status register 2                                           | 0x0         |

| INTEN2             | 0xbfd0 0174 | R/W                         | Interrupt enable register 2                                           | 0x0         |

| INTSET2            | 0xbfd0 0178 | R/W                         | Interrupt setting register 2                                          | 0x0         |

| INTCLR2            | 0xbfd0 017c | R/W                         | Interrupt clear register 2                                            | 0x0         |

| INTPOL2            | 0xbfd0 0180 | R/W                         | Interrupt triggering level flag<br>register 2                         | 9<br>0x0    |

| INTEDGE2           | 0xbfd0 0184 | R/W                         | Interrupt triggering edge flag<br>register 2                          |             |

| INTISR3            | 0xbfd0 0188 | R                           | Interrupt status register 3                                           | 0x0         |

| INTEN3             | 0xbfd0_018c | R/W                         | Interrupt enable register 3                                           | 0x0         |

| INTSET3            | 0xbfd0 0190 | R/W                         | Interrupt setting register 3                                          | 0x0         |

| INTCLR3            | 0xbfd0_0194 | R/W                         | Interrupt clear register 3                                            | 0x0         |

| INTPOL3            | 0xbfd0_0198 | R/W                         | Interrupt triggering level flag<br>register 3                         |             |